## University of Global Village (UGV), Barishal Dept. of Electrical and Electronic Engineering (EEE)

# Digital Electronics (EEE 0714-2101) Digital Logic Design (CSE 0611-1201)

Noor Md Shahriar

Senior Lecturer, Deputy Head of Dept.

Dept. of Electrical & Electronic Engineering University of Global Village, (UGV), Barishal

Contact: 01743-500587

E-mail: noor.shahriar1@gmail.com

'Imagination is more important than knowledge

- Albert Einstein

## **Basic Course Information**

| Course Title        | Digital Electronics/ Digital Logic Design        |  |

|---------------------|--------------------------------------------------|--|

| Course Code         | EEE- 0714-3107                                   |  |

| Credits             | 03                                               |  |

| CIE Marks           | 90                                               |  |

| SEE Marks           | 60                                               |  |

| Exam Hours          | 2 hours (Mid Exam) 3 hours (Semester Final Exam) |  |

| Level               | 4 <sup>th</sup> Semester  Summer 2025            |  |

| Academic<br>Session |                                                  |  |

## Digital Electronics (EEE-0714-2109)

#### 3 Credit Course

Class: 17 weeks (2 classes per week)

**Total Class Duration: 1 hrs.**

**Total=34 Hours**

Preparation Leave (PL): 02 weeks

Exam: 04 weeks

Results: 02 weeks

Total: 25 Weeks

#### Attendance:

Students with more than or equal to 70% attendance in this course will be eligible to sit for the Semester End Examination (SEE). SEE is mandatory for all students.

Continuous Assessment

Strategy

Altogether 4 quizzes may be taken during the semester, 2 quizzes will be taken for midterm and 2 quizzes will be taken for final term.

Altogether 2 assignments may be taken during the semester, 1 assignments will be taken for midterm and 1 assignments will be taken for final term.

The students will have to form a group of maximum 3 members. The topic of the presentation will be given to each group and students will have to do the group presentation on the given topic.

#### **ASSESSMENT PATTERN**

CIE- Continuous Internal Evaluation (90 Marks)

SEE- Semester End Examination (60 Marks)

| Bloom's<br>Category<br>Marks<br>(out of 90) | Tests (45) | Quizzes<br>(15) | External Participation in Curricular/Co- Curricular Activities (15) |

|---------------------------------------------|------------|-----------------|---------------------------------------------------------------------|

| Remember                                    | 08         | 08              | Bloom's Affective                                                   |

| Understand                                  | 08         | 07              | Domain: (Attitude or will)                                          |

| Apply                                       | 08         |                 | Attendance: 15                                                      |

| Analyze                                     | 08         |                 | Copy or attempt to copy: -10 Late                                   |

| Evaluate                                    | 08         |                 | Assignment: -10                                                     |

| Create                                      | 05         |                 |                                                                     |

| Bloom's    | Tests |

|------------|-------|

| Category   |       |

| Remember   | 10    |

| Understand | 10    |

| Apply      | 10    |

| Analyze    | 10    |

| Evaluate   | 10    |

| Create     | 10    |

## Course Learning Outcome (CLO)

| Serial No. | Course Learning Outcome (CLO)                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLO-1      | <b>Understand</b> and <b>recall</b> the process of minimization through K-mapping and tabular method.                                                                  |

| CLO-2      | <b>Analyze</b> and <b>construct</b> combinational circuits and sequential circuits using Logic Gates.                                                                  |

| CLO-3      | <b>Explain</b> and <b>Examine</b> memory elements using circuits.                                                                                                      |

| CLO-4      | Construct combinational and sequential circuits through VHDL by understanding dataflow, behavioral and structural modeling, synthesis and simulation of both circuits. |

## SYNOPSIS / RATIONALE

■ The Digital Electronics course provides EEE students with fundamental knowledge of digital systems, covering topics like Boolean algebra, logic gates, combinational and sequential circuits, and flip-flops. It equips students with the skills to analyze, design, and optimize digital circuits, which are essential in modern computing, communication systems, automation, and embedded technologies. By bridging theoretical concepts with practical applications, the course prepares students for advanced studies in microprocessors, VLSI, and digital signal processing, ensuring they are ready to tackle industry challenges and innovate in emerging technologies.

## Course objectives

- To introduce the fundamental concepts of digital logic and Boolean algebra.

- To enable students to analyze and design combinational circuits using logic gates.

- To provide an understanding of sequential circuits, flip-flops, and their applications.

- To develop the ability to implement and troubleshoot digital circuits in practical scenarios.

- To prepare students for advanced topics like microprocessors, VLSI, and digital signal processing.

- To enhance problem-solving skills for designing optimized digital systems used in modern electronics and communication technologies.

Digital Logic Design

**Digital Electronics**

Lectures: 3 hours/week

Credits: 3

| Seria<br>1 No. | Content of Course                                                                                                                                                                                                                                                           | Hour<br>s | CLOs            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| 1              | Analysis and Synthesis of Digital Logic Circuits: Number system, codes, and conversion. Boolean algebra, De Morgan's law, logic gates and truth tables, combinational logic design, minimization techniques, implementation of basic static logic gates in CMOS and BiCMOS. | 9         | CLO-1,<br>CLO-2 |

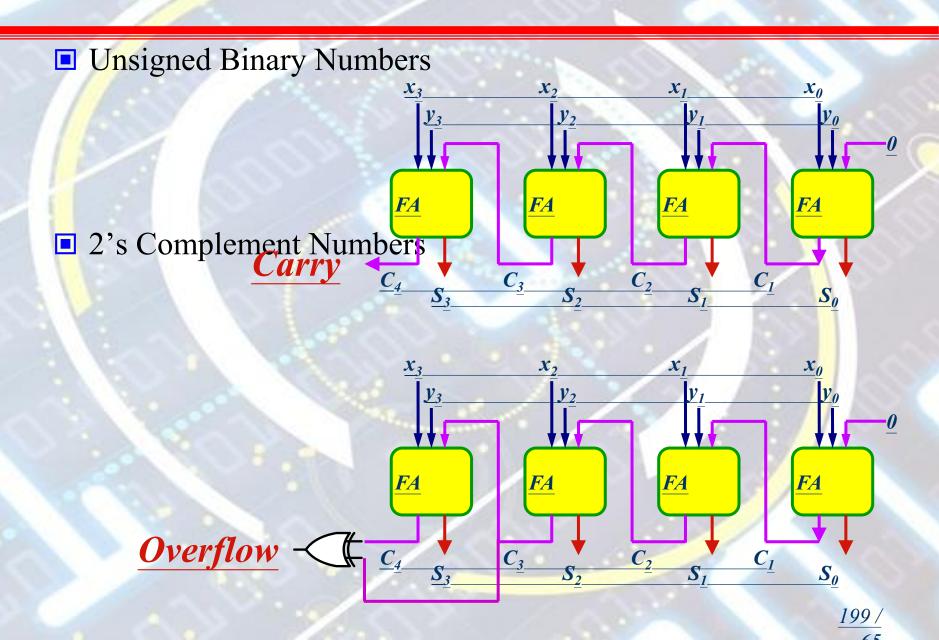

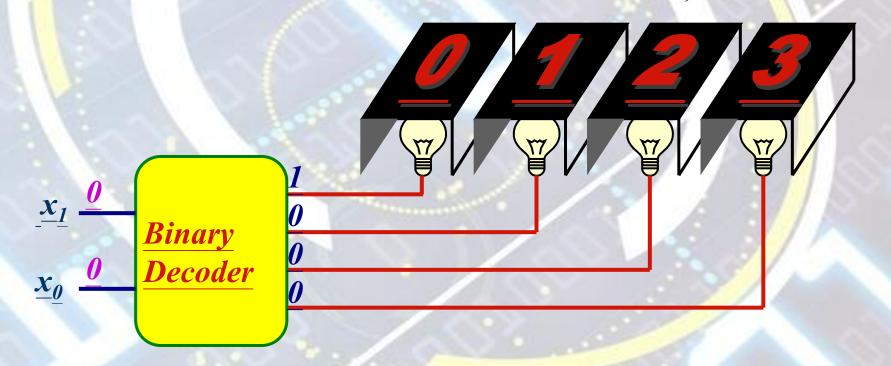

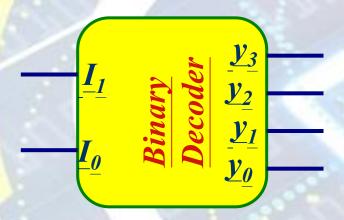

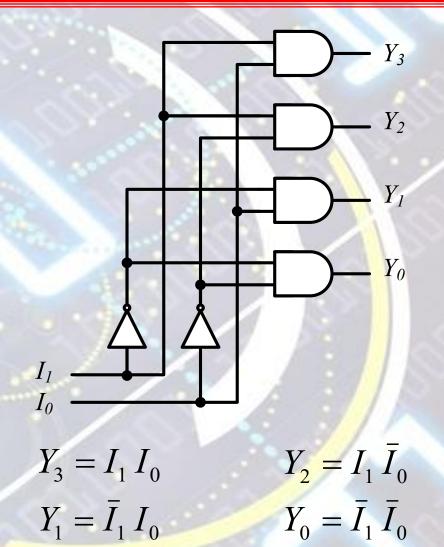

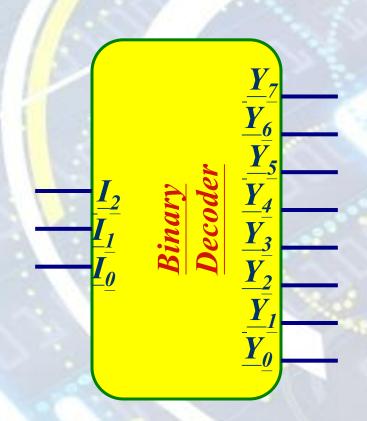

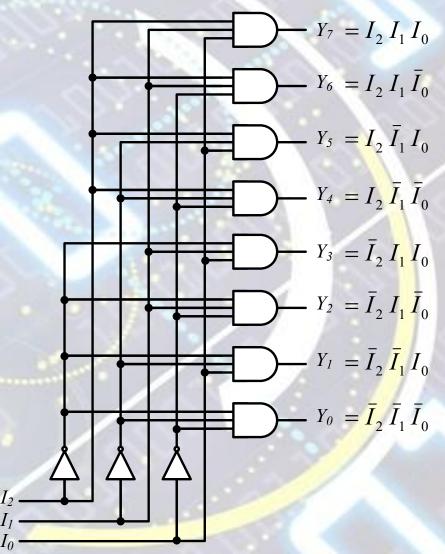

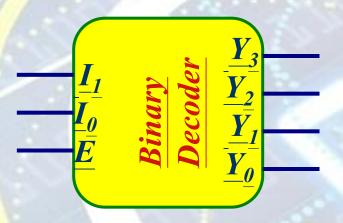

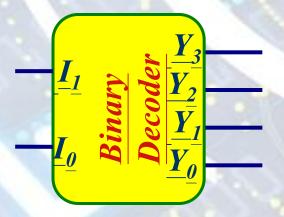

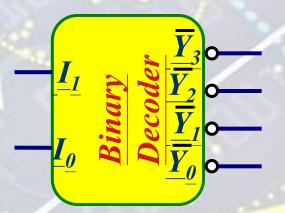

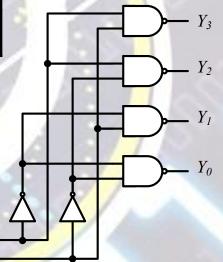

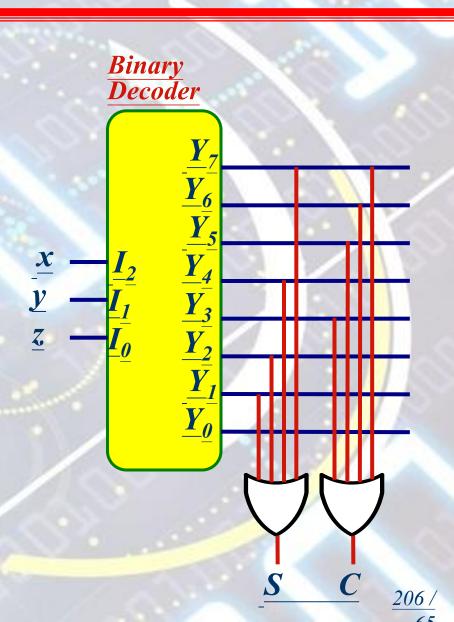

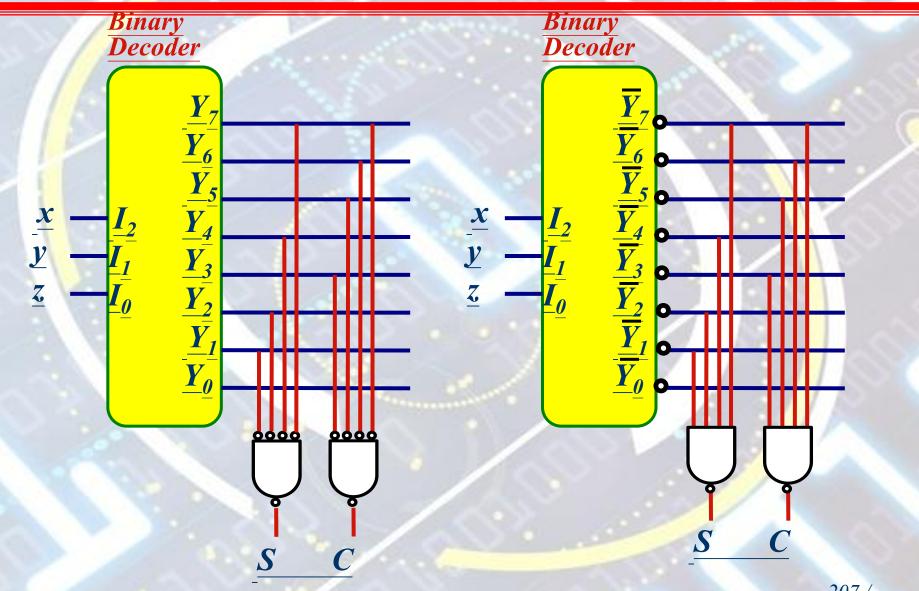

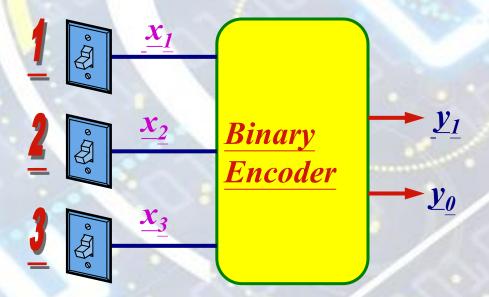

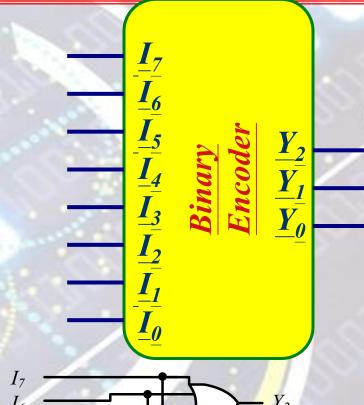

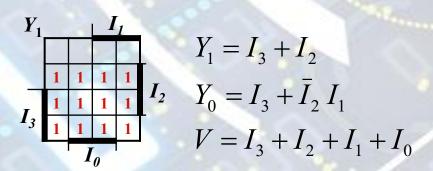

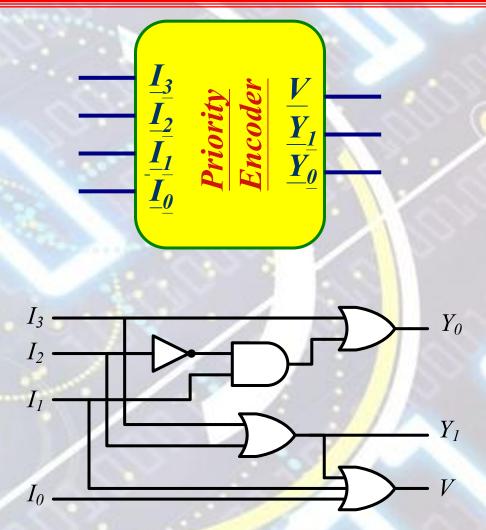

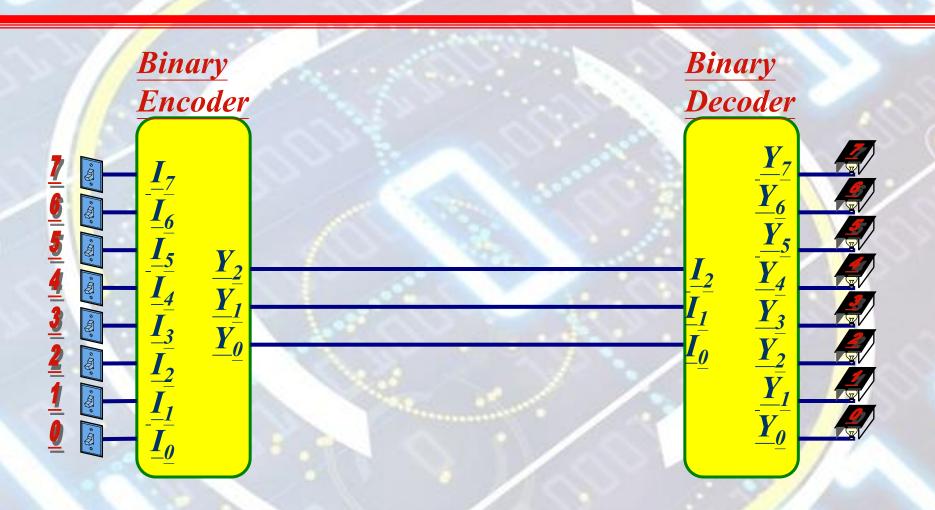

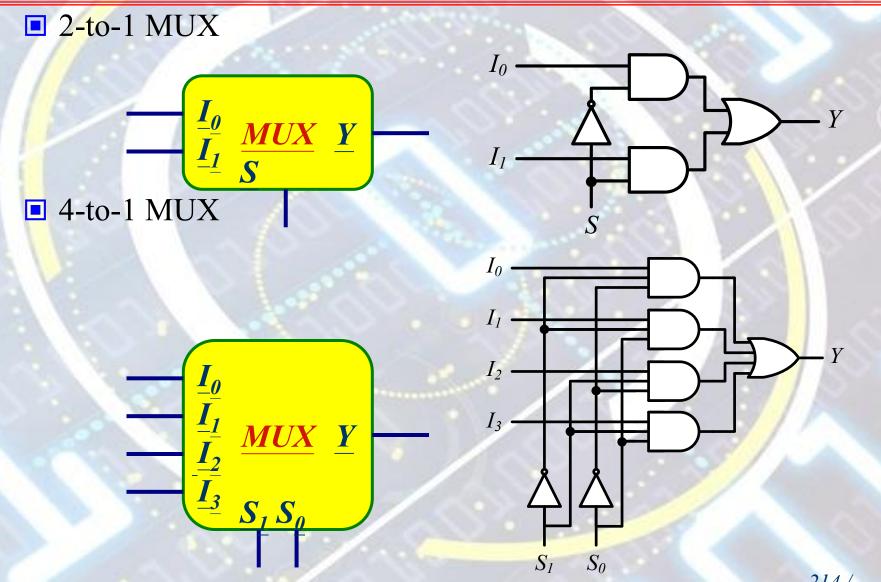

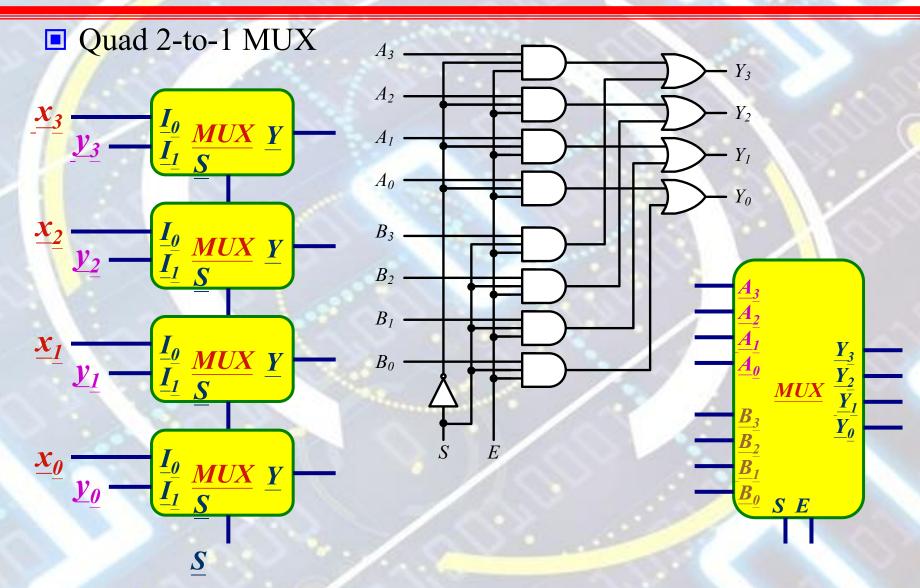

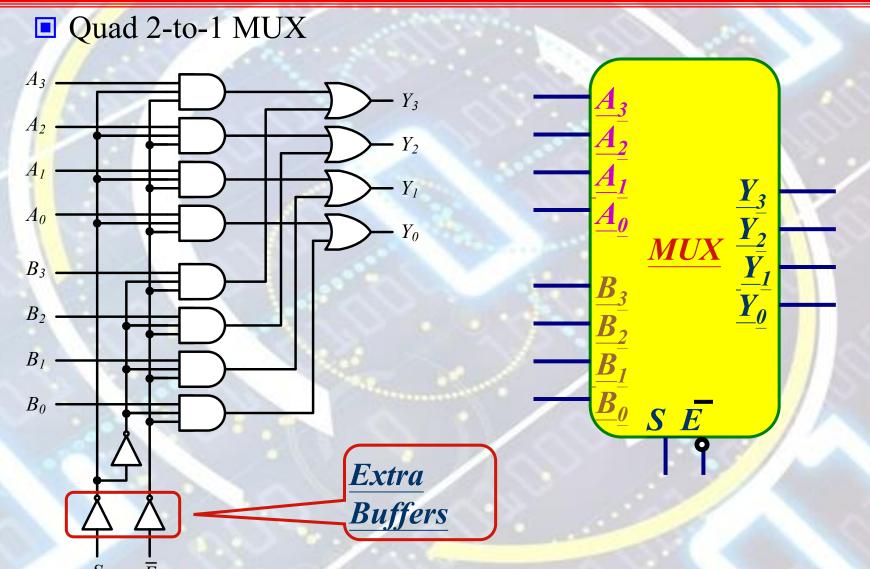

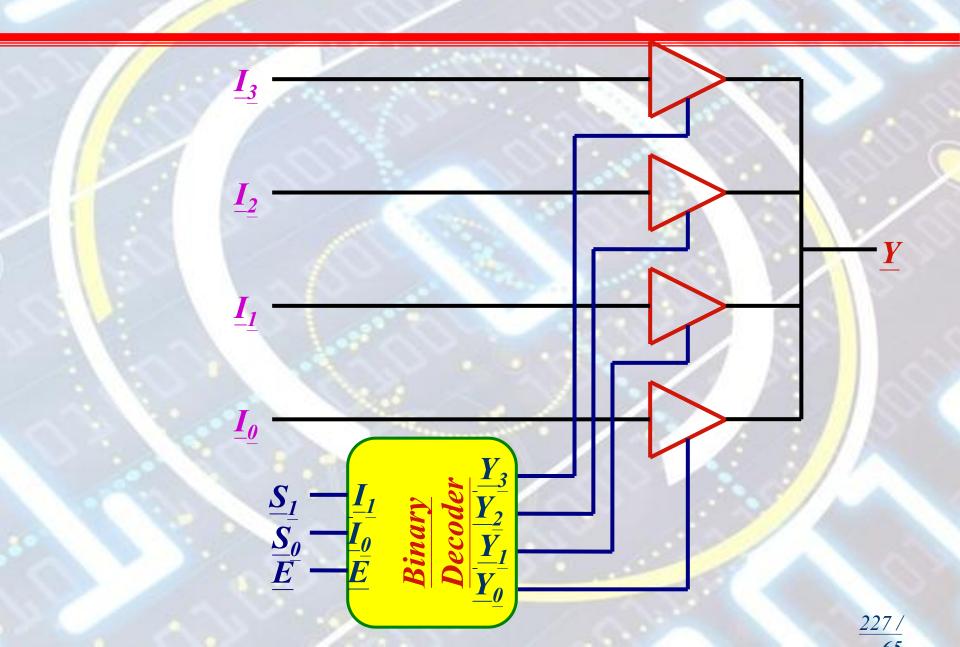

| 2              | Arithmetic and data handling logic circuits, decoders and encoders, multiplexers and combinational circuit design.                                                                                                                                                          | 8         | CLO-2,<br>CLO-3 |

| 3              | <b>Programmable Logic Devices</b> : Logic arrays, Field Programmable Logic Arrays, and Programmable Read Only Memory.                                                                                                                                                       |           | CLO-3,<br>CLO-4 |

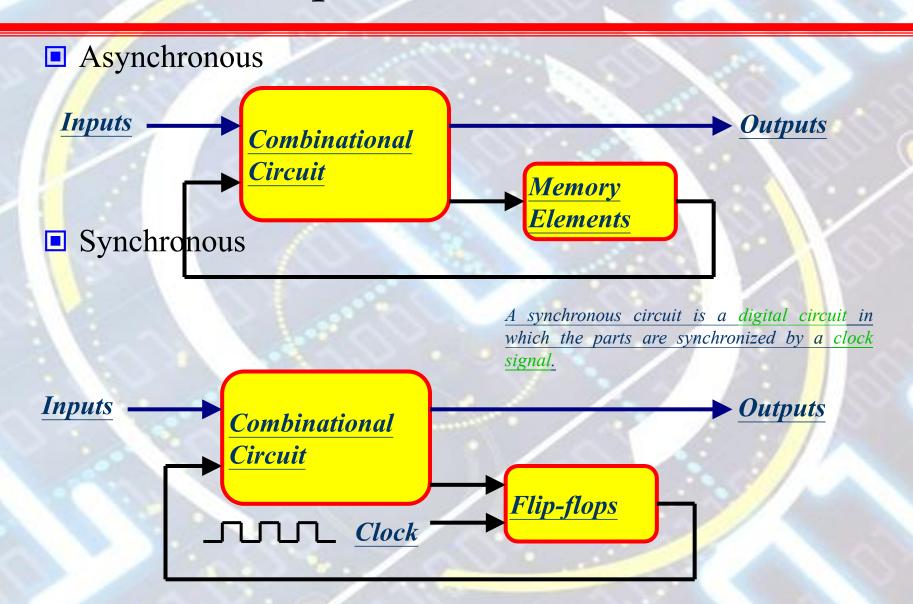

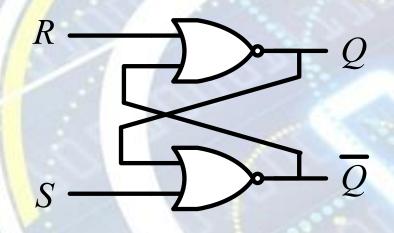

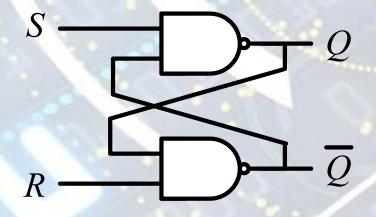

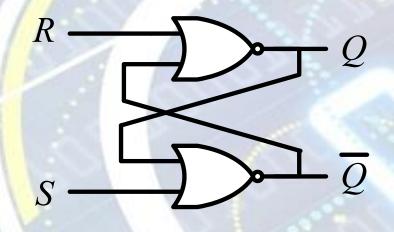

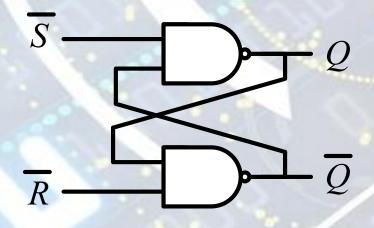

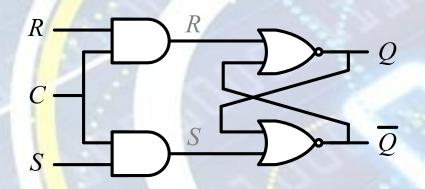

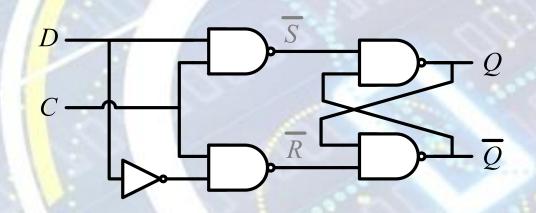

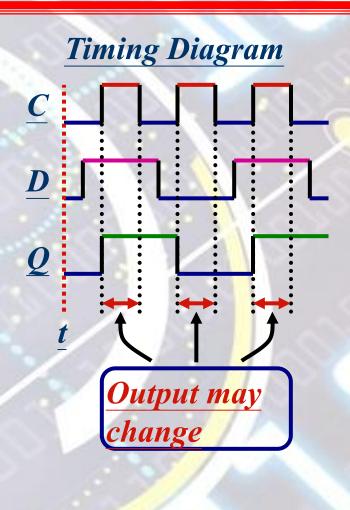

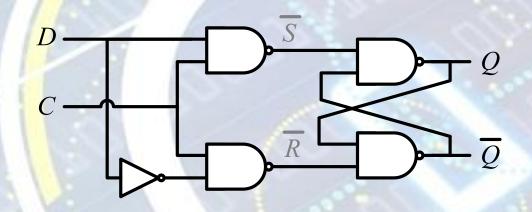

| 4              | <b>Sequential Circuits</b> : Different types of latches, flip-flops and their design using ASM approach, timing analysis, and power optimization of sequential circuits.                                                                                                    |           | CLO-3,<br>CLO-4 |

| 5              | Modular sequential logic circuit design: Shift registers, counters and their applications.                                                                                                                                                                                  | 8         | CLO-4           |

#### Course Schedule

Course plan specifying content, CLOs, teaching learning and assessment strategy mapped with CLOs

| Week | Content of Course                                                                                                                                                           | ASG/<br>Quiz/<br>Pr | Teaching-<br>Learning<br>Strategy            | Assessment<br>Strategy                  | Corres-<br>ponding<br>CLOs |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------|-----------------------------------------|----------------------------|

| 1    | Introduction to Digital Electronics, Basic idea about Analog and Digital signals. Details about various types of number systems.                                            |                     | Lecture,<br>Discussion                       | Written Exam,<br>Class<br>Participation | CLO-1                      |

|      | Converting base of integer and fractional numbers from one number system to another.                                                                                        |                     | Lecture, Group<br>Examples                   | Classwork,<br>Problem Solving           | CLO-1                      |

| 2    | Data Representation and Complements.                                                                                                                                        | Quiz-1              | Lecture, Visual<br>Aids, Group<br>Discussion | Quiz, Written<br>Exam                   | CLO-1                      |

| 3    | Addition and Subtraction operation of Binary, Octal & Hexadecimal Numbers.                                                                                                  | ASG                 | Lecture,<br>Practice<br>Problems             | Assignment,<br>Problem Solving          | CLO-2                      |

| 4    | Negative binary number representation in various methods and basic idea about complements. Subtraction of other number systems using Radix and Diminished Radix complement. |                     | Lecture, Group<br>Problem<br>Solving         | Written Exam,<br>Group<br>Discussion    | CLO-2<br><u>10</u>         |

## Course Schedule (Contd.)

|   | 5 | Introduction to different types of binary codes. Weighted codes, Gray code, ASCII code, and error-detecting code.             | Quiz-2         | Lecture, Case<br>Studies,<br>Problem<br>Practice    | Quiz, Problem-<br>Solving           | CLO-3 |

|---|---|-------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------|-------------------------------------|-------|

| Y | 6 | Definition of Boolean algebra,<br>Boolean theorems, and De-<br>Morgan's theorem.<br>Simplification using theorems.            | Assign<br>ment | Lecture,<br>Hands-on<br>Examples,<br>Practical Work | Assignment,<br>Oral<br>Presentation | CLO-3 |

|   | 7 | Simplification of Boolean<br>Algebra, Properties & K-Map<br>Method                                                            |                | Lecture, Board<br>Work,<br>Practical<br>Examples    | Problem<br>Solving,<br>Classwork    | CLO-4 |

|   | 8 | Binary Logic, AND, OR, NOT,<br>NAND, NOR, X-OR, and X-<br>NOR gates. Formation of<br>Boolean algebra using universal<br>gates | Quiz-3         | Lecture, Case<br>Studies,<br>Practical Work         | Quiz, Problem<br>Solving            | CLO-3 |

|   | 9 | Gate Level Minimization,<br>Boolean Functions, Truth Table,<br>Canonical Forms                                                |                | Lecture, Group Activities, Hands-on Examples        | Written Exam,<br>Practical Tasks    | CLO-  |

## Course Schedule (Contd.)

| Wee<br>k | Content of Course                                                    | ASG<br>/Qui<br>z/Pr  | Teaching-<br>Learning<br>Strategy                 | Assessment<br>Strategy                    | Corresponding CLOs |

|----------|----------------------------------------------------------------------|----------------------|---------------------------------------------------|-------------------------------------------|--------------------|

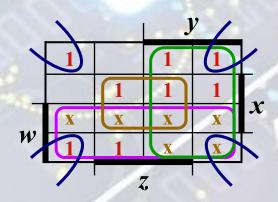

| 10       | Combinational Logic<br>Analysis, K-Map with Don't<br>Care Conditions | Mid-<br>Term<br>Exam | Lecture, Board Examples, Group Practice           | Mid-Term Exam                             | CLO-4              |

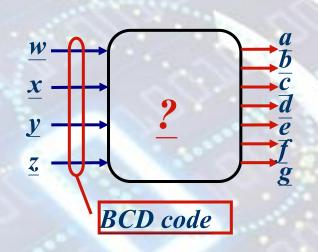

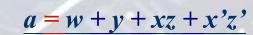

| 11       | BCD to excess 3 and Seven<br>Segment Decoder                         |                      | Lecture, Problem- Solving Activities              | Written Exam,<br>Problem Solving          | CLO-5              |

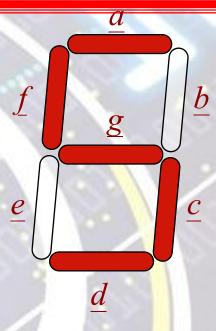

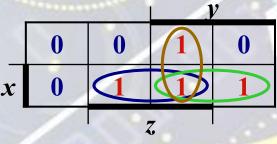

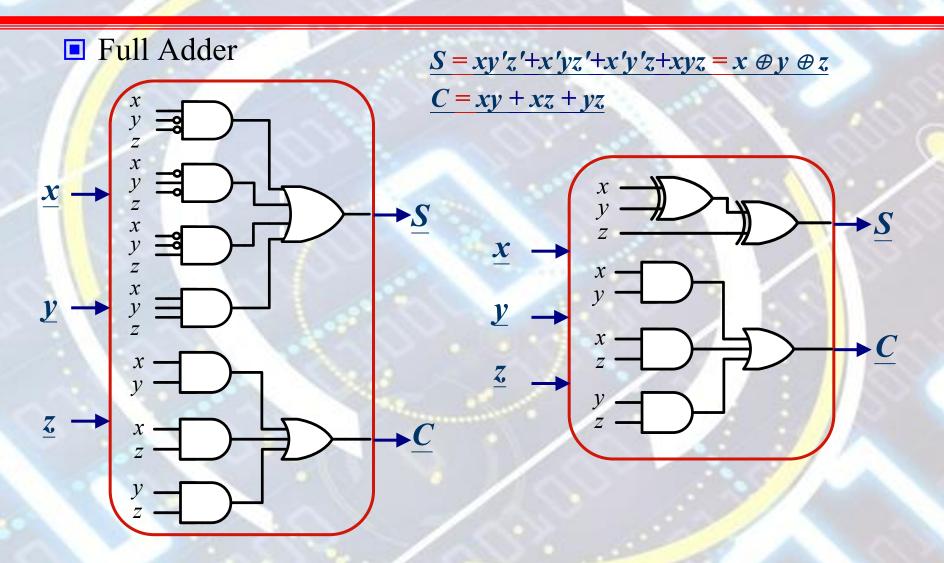

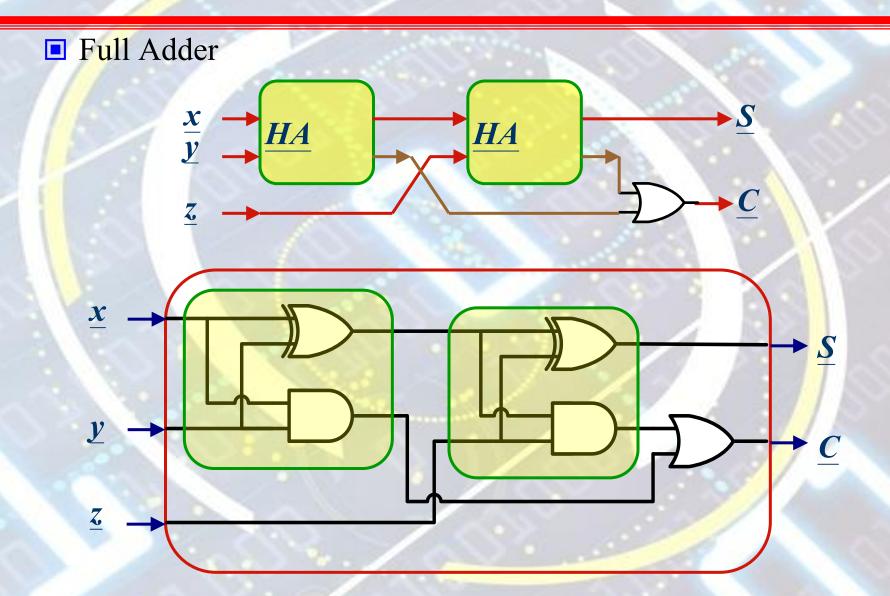

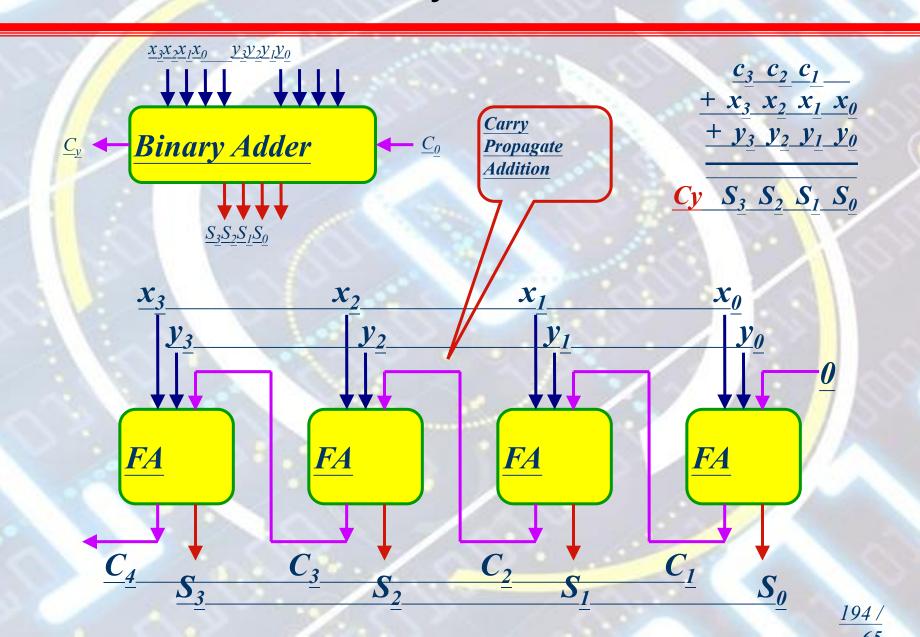

| 12       | Half adder, full adder, and<br>subtractor design, encode,<br>decoder | ASG                  | Lecture,<br>Visual Aids,<br>Practical<br>Examples | Assignment, Oral<br>Presentation          | CLO-5              |

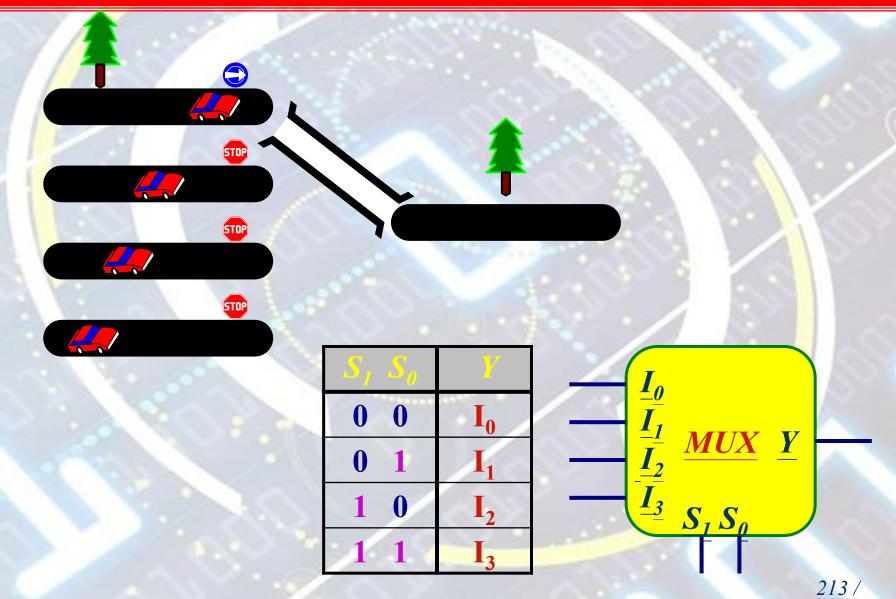

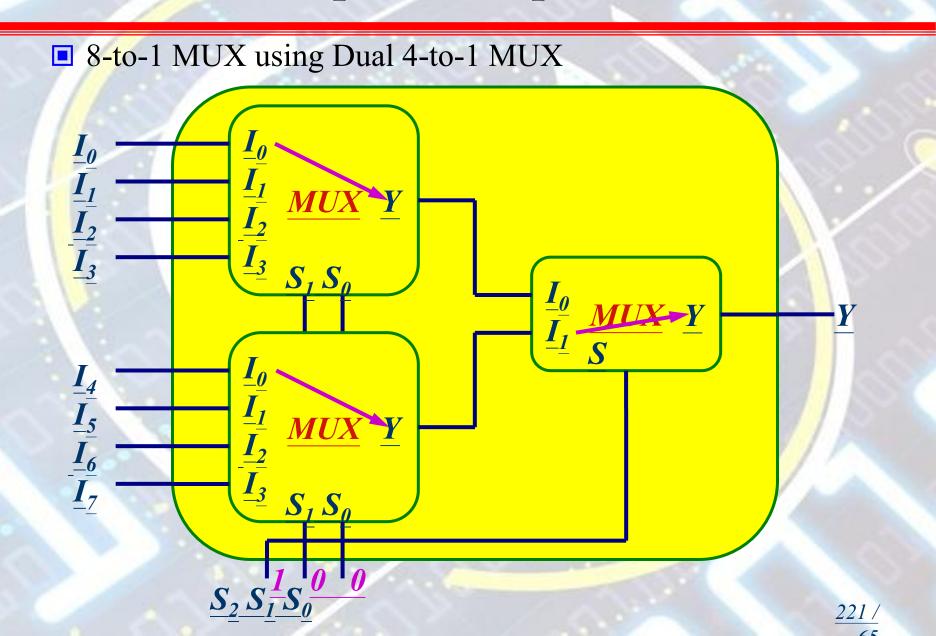

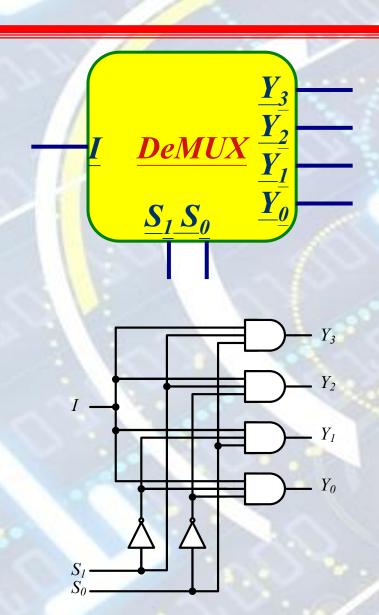

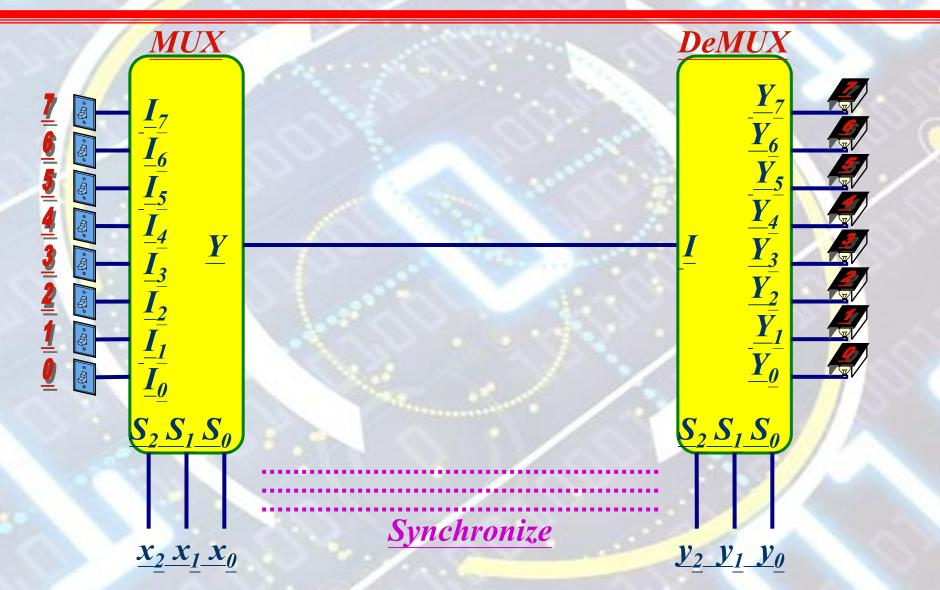

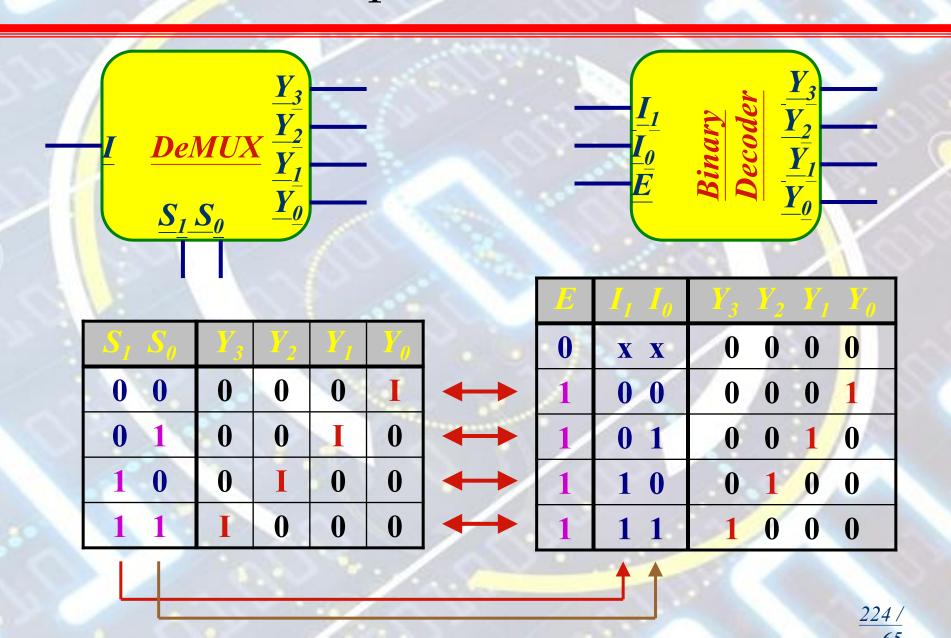

| 13       | Design of Muxtiplexer ,<br>demultiplexer                             |                      | Lecture,<br>Group<br>Examples,<br>Case Studies    | Written Exam,<br>Group Problem<br>Solving | CLO-5              |

## Course Schedule (Contd.)

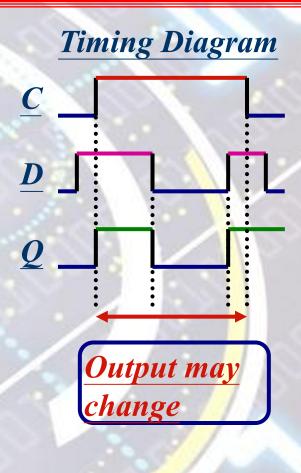

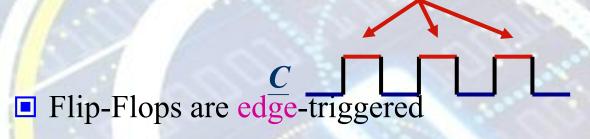

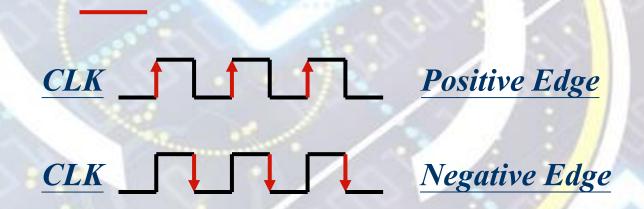

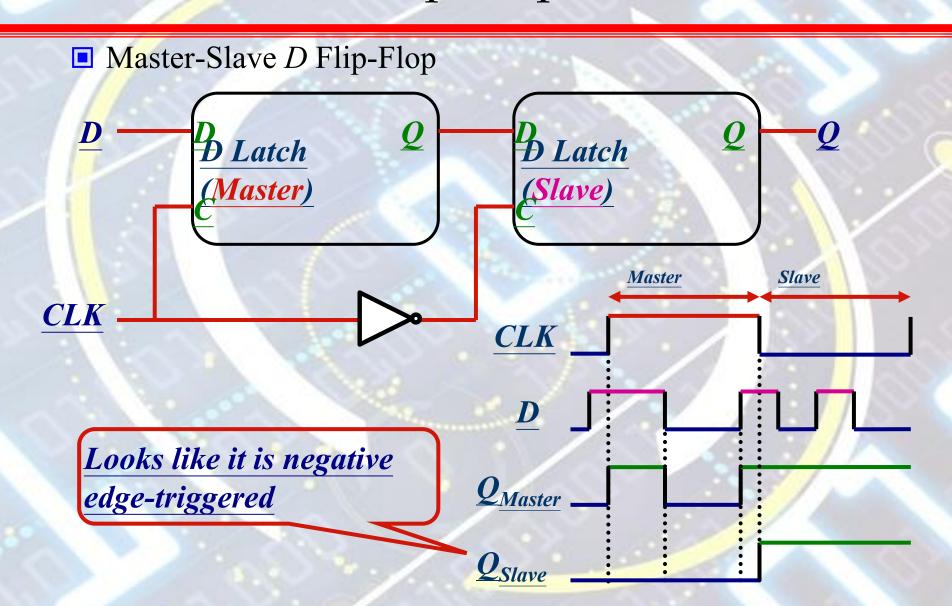

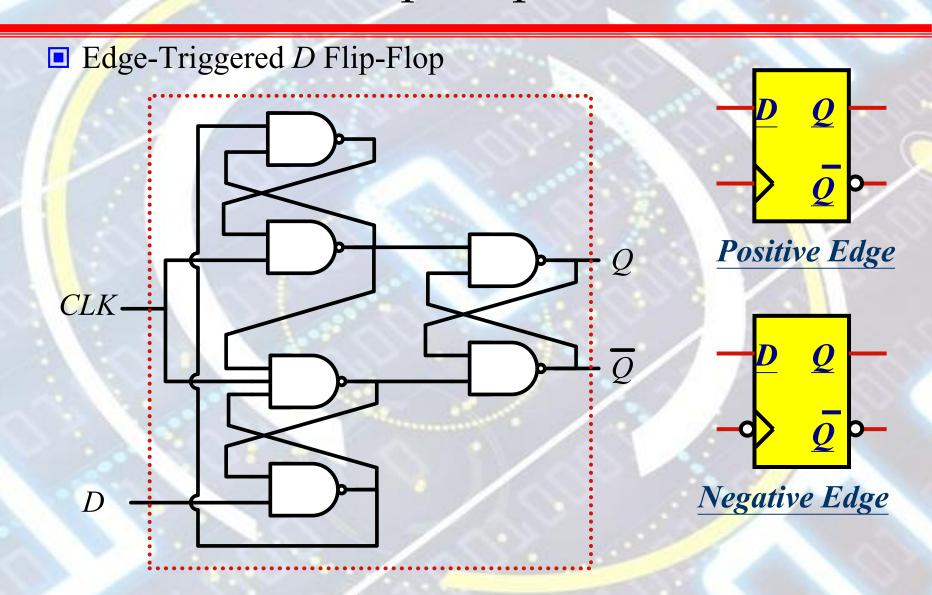

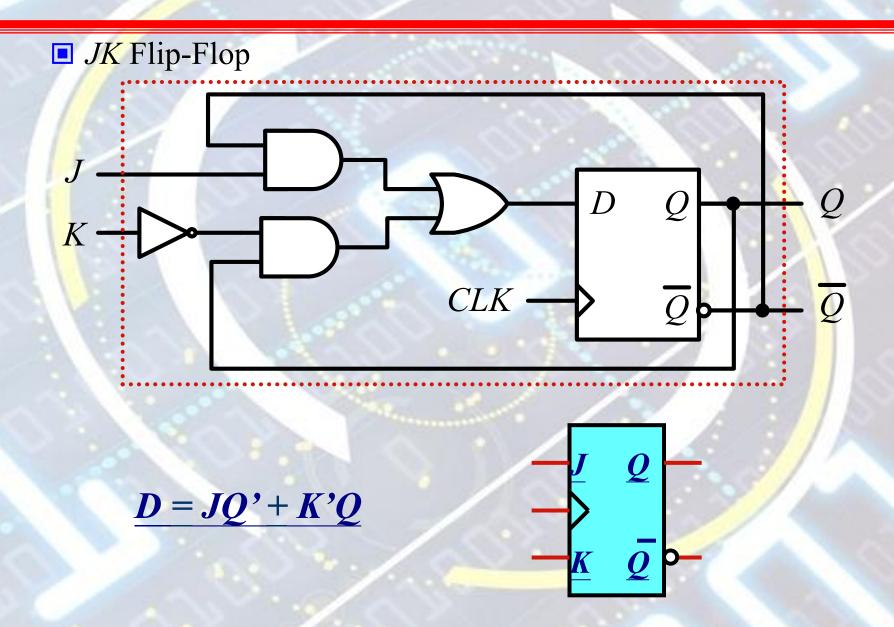

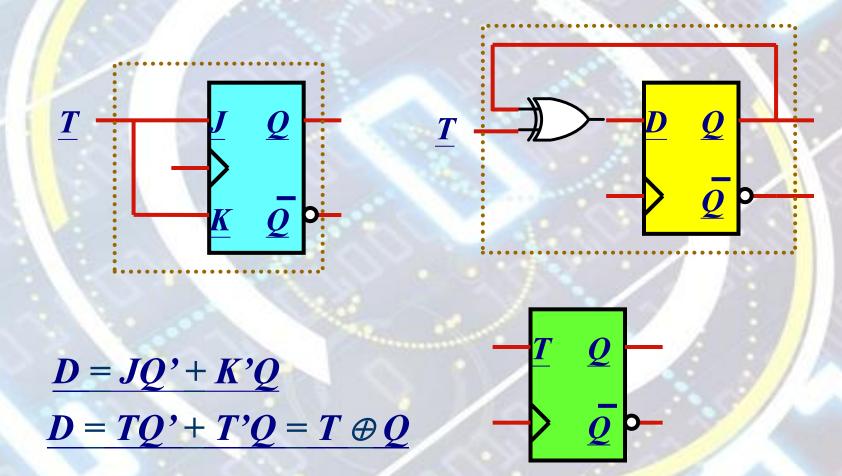

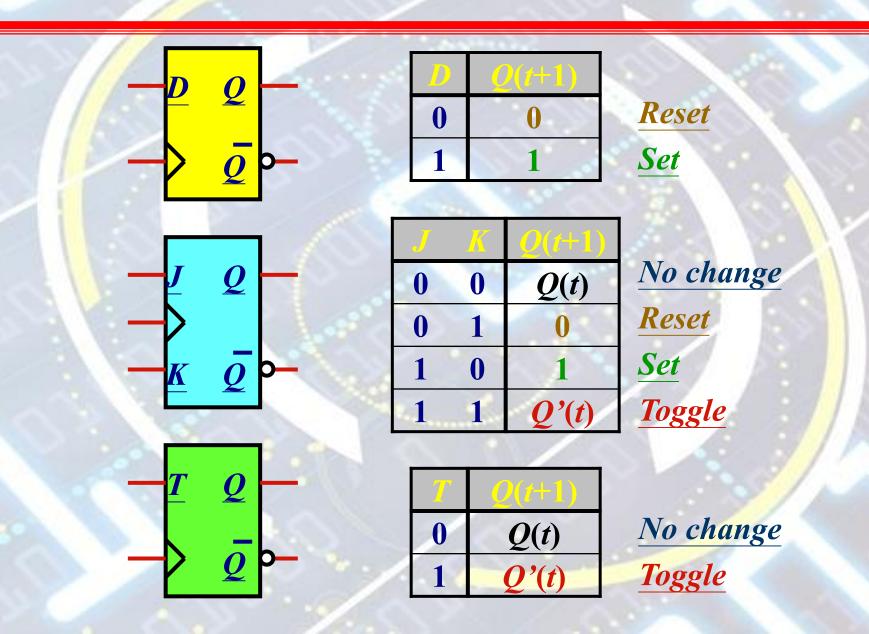

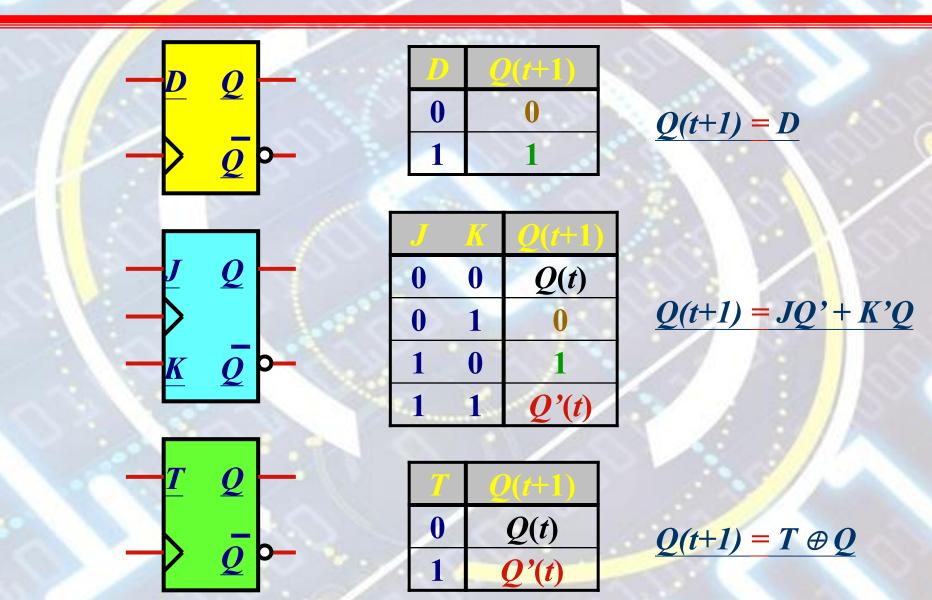

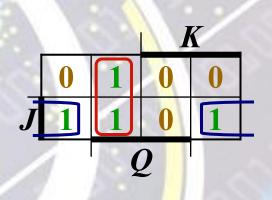

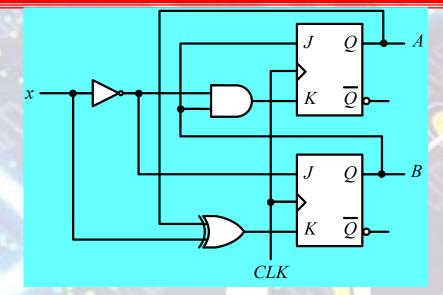

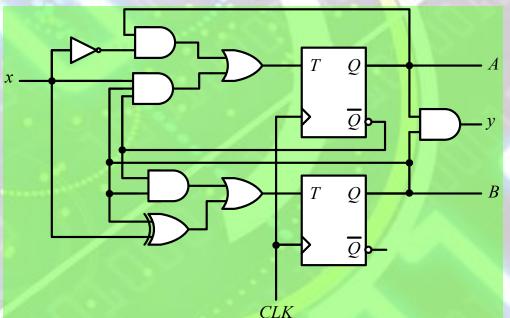

| 14 | SR, D, JK and T flipflops<br>,Master-Slave flip-flop and<br>Edge Triggered circuits.<br>Conversion of Flip-flops. |            | Lecture, Practical Examples, Group Discussion            | Problem Solving,<br>Assignment      | CLO-5 |

|----|-------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------|-------------------------------------|-------|

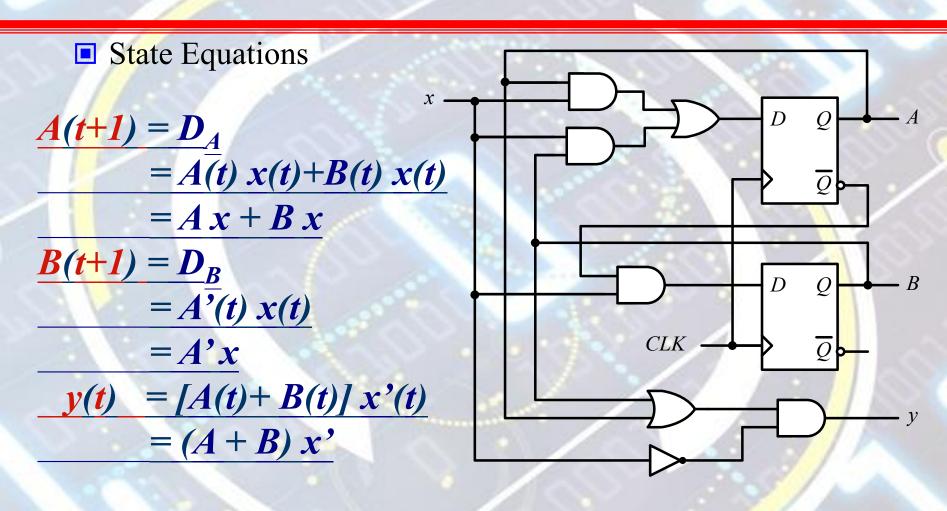

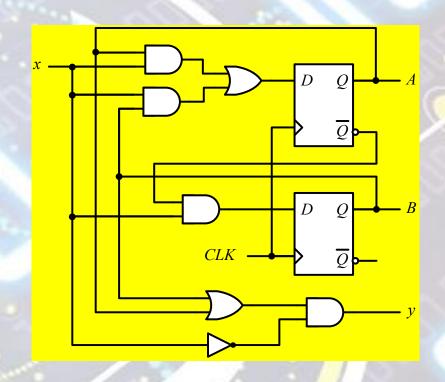

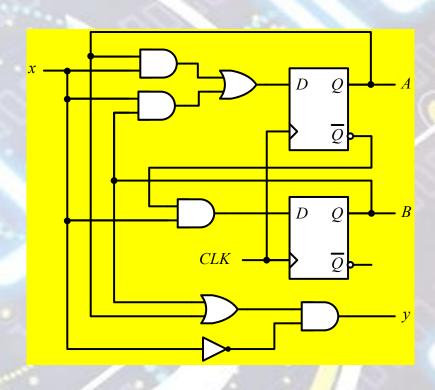

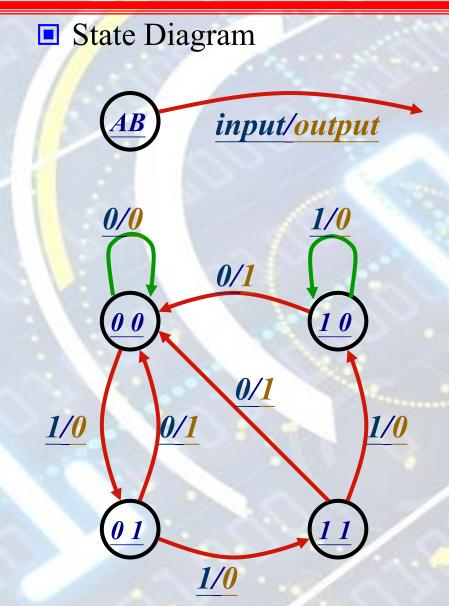

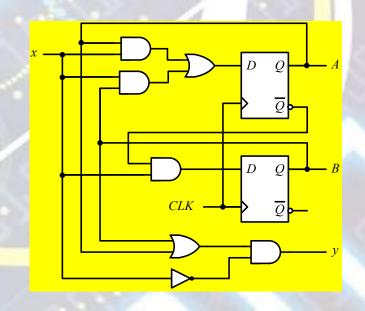

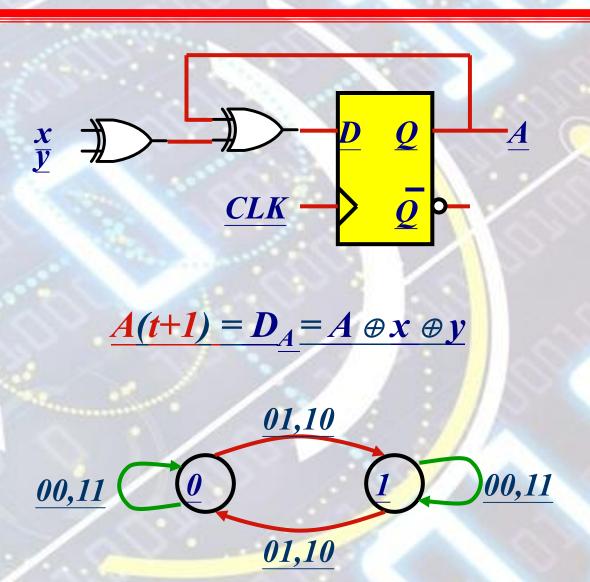

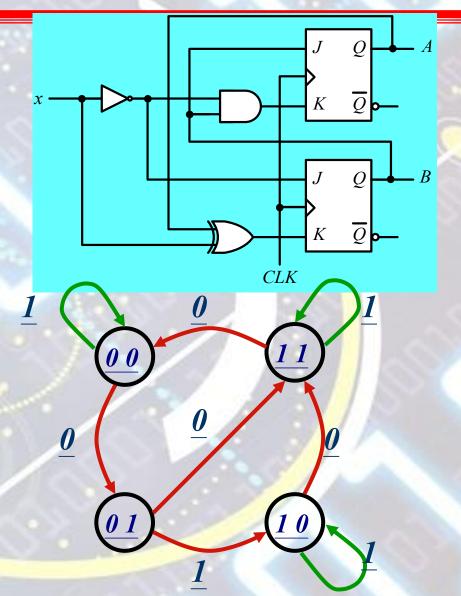

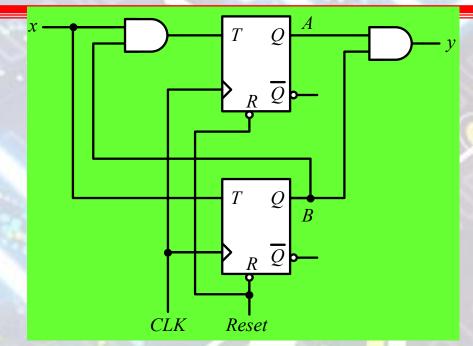

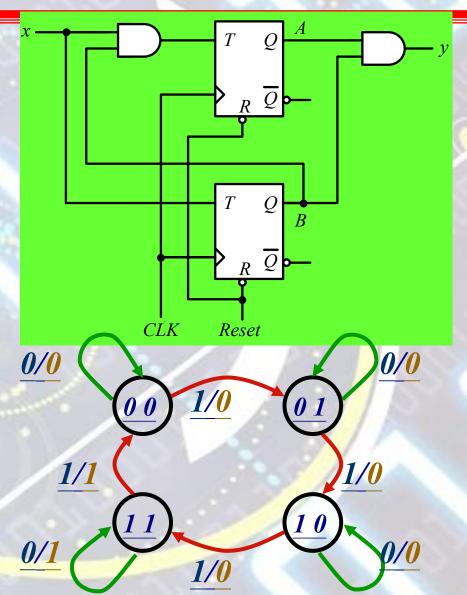

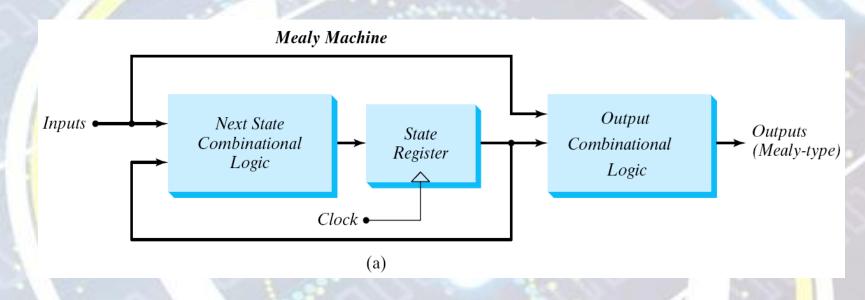

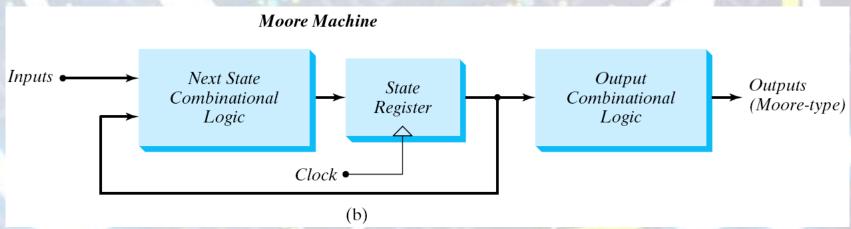

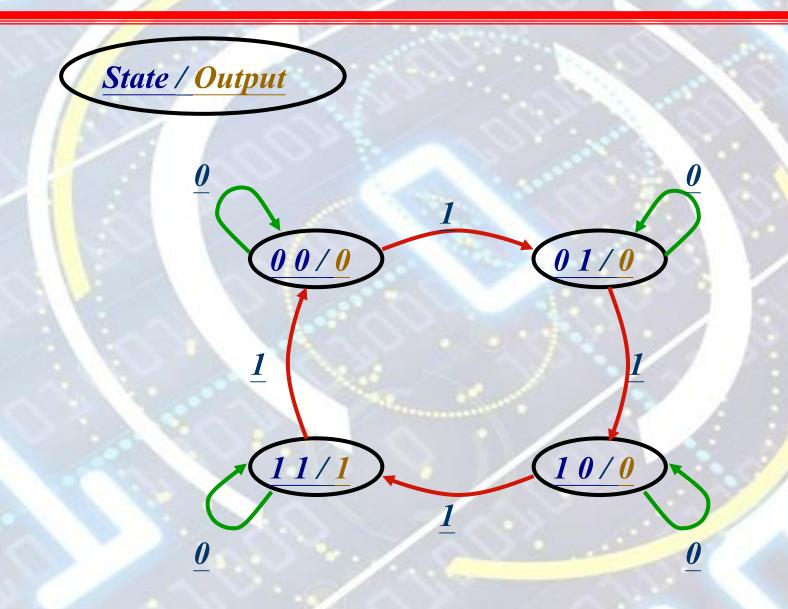

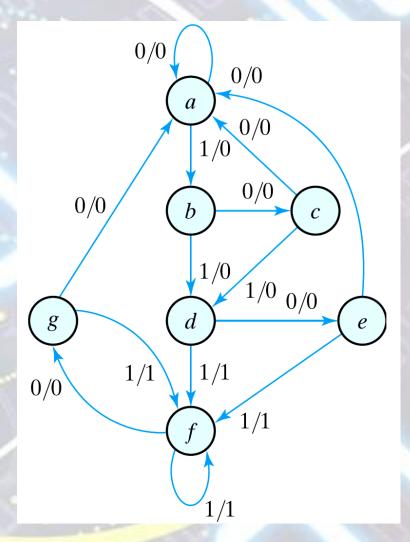

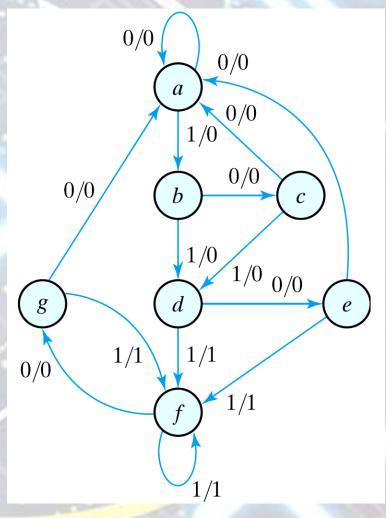

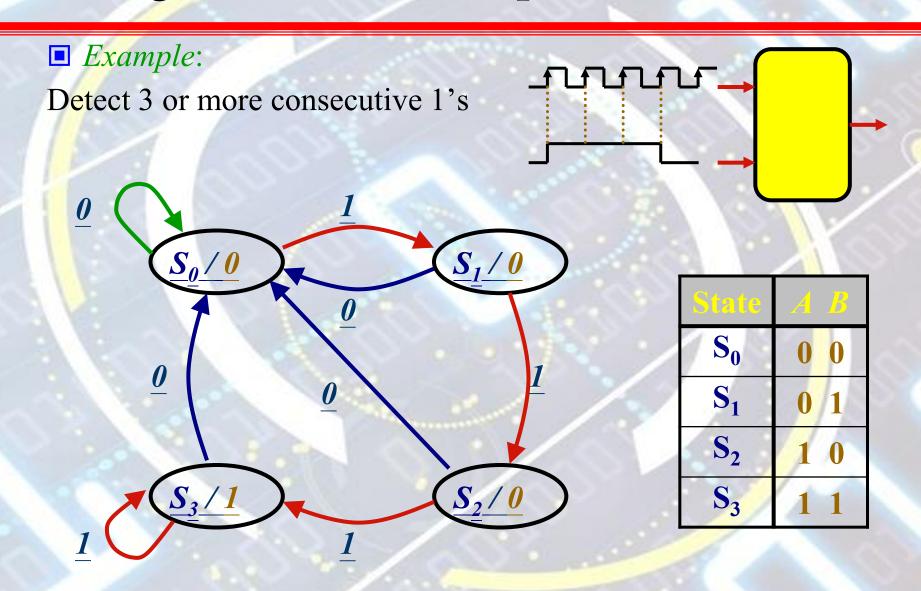

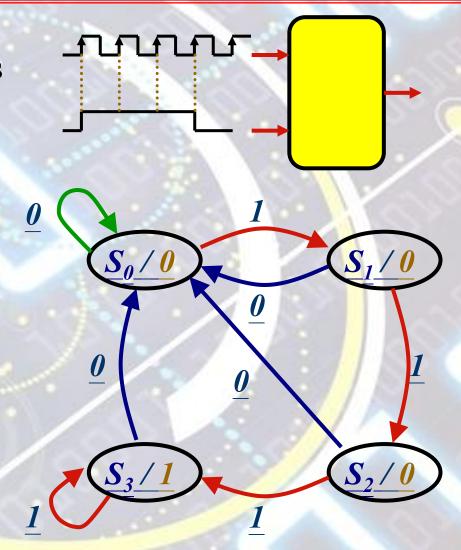

| 15 | State Table, State Diagram,<br>Mealy and Moore machines.                                                          | Quiz-<br>4 | Lecture, Case<br>Studies,<br>Group<br>Problem<br>Solving | Quiz, Written<br>Exam               | CLO-5 |

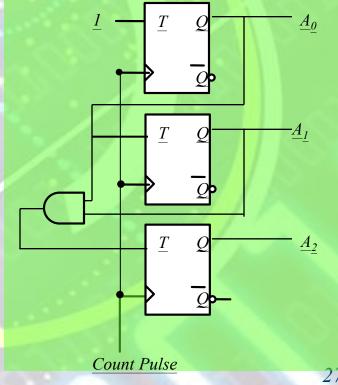

| 16 | Counters: Asynchronous and Synchronous Counters, Up/Down Counters.                                                |            | Lecture, Practical Examples, Visual Aids                 | Assignment,<br>Written Exam         | CLO-6 |

| 17 | Ring Counter, Johnson<br>Counter, Design of<br>Sequential Circuits.                                               |            | Lecture, Group Activities, Hands-on Examples             | Problem Solving,<br>Practical Tasks | CLO-6 |

#### REFERENCE BOOK

Digital Logic Design 10<sup>th</sup> Edition By Tocci

#### Video Lecture Playlist

https://youtube.com/playlist?list=PLbfLO9aEfT5f

pYgbTlQKxo4jiwbEADayG&si=1ay1sarJsBxnPn

qV

#### **Basic Definition**

- Digital Logic Design is the study and

- implementation of electronic circuits that process information using binary digits (0 and 1), known as digital signals. It involves:

- •Designing circuits using logic gates (AND, OR, NOT, etc.).

- Understanding Boolean algebra.

- Constructing systems like adders, multiplexers, counters,

memory units, and finite state machines.

## Why study this subject?

|                      | Skill/Knowledge            | <b>Enabled By Digital Logic</b> |

|----------------------|----------------------------|---------------------------------|

|                      | System-level               | Learn how code runs on          |

|                      | understanding              | hardware                        |

|                      | Problem-solving and        | Logic circuit design mirrors    |

|                      | design                     | algorithm development           |

|                      | Embedded & IoT             | Essential for microcontroller   |

|                      | development                | interfacing                     |

| Hardware programming |                            | Verilog/FPGA, VLSI, HDL-        |

| ١                    | Tiaraware programming      | based design                    |

|                      | Secure system design       | Digital lock, authentication,   |

| Secure system design |                            | cryptographic hardware          |

|                      | Performance optimization   | Custom logic for acceleration   |

|                      | r criorinance optimization | (e.g., ML chips, DSP blocks) 17 |

#### Consumer Electronics

- Digital watches and clocks

- Washing machines, microwave ovens, remote controls

- Smart TVs, audio systems

#### Computers and Embedded Systems

- CPU and GPU architecture

- Memory (RAM/ROM) management

- Instruction decoders and control units

#### Communication Systems

- Modulation/demodulation logic (e.g., QAM, FSK)

- Error detection and correction circuits (parity, Hamming code)

- Multiplexers in channel selection

#### **■** Automotive Systems

- Engine control units (ECUs)

- Parking sensors and collision avoidance systems

- Digital dashboards and infotainment units

#### Medical Devices

- Digital thermometers and ECG machines

- Patient monitoring systems

- Diagnostic imaging control circuits

#### Industrial Automation

- Programmable Logic Controllers (PLCs)

- Robotic control logic

- Conveyor belt and sorting system control

#### Security Systems

- Digital locks and access control

- Motion detection and alarm logic

- Biometric interface logic (FPGA-based)

#### Aerospace and Defense

- Flight control systems (redundant FSM-based designs)

- Radar signal processing

- Secure communication protocols

#### Networking and Data Centers

- Packet routing and switching logic

- Data buffering and FIFO/LIFO logic circuits

- Traffic prioritization algorithms (digital logic level)

#### Signal and Image Processing

- Digital filters and convolution logic

- Real-time image edge detection

- Compression algorithms (DCT, Huffman coding)

#### **■** Internet of Things (IoT)

- Sensor interfacing and signal conditioning

- Power-efficient logic control

- Edge computing controllers

#### **■** Gaming and Entertainment

- Gamepad/button logic

- Display controllers (LCD/LED driving logic)

- Audio synthesis and timing circuits

## Outline of Chapter 1

- 1.1 Digital Systems

- 1.2 Binary Numbers

- 1.3 Number-base Conversions

- 1.4 Octal and Hexadecimal Numbers

- 1.5 Complements

- 1.6 Signed Binary Numbers

- 1.7 Binary Codes

- 1.8 Binary Storage and Registers

- 1.9 Binary Logic

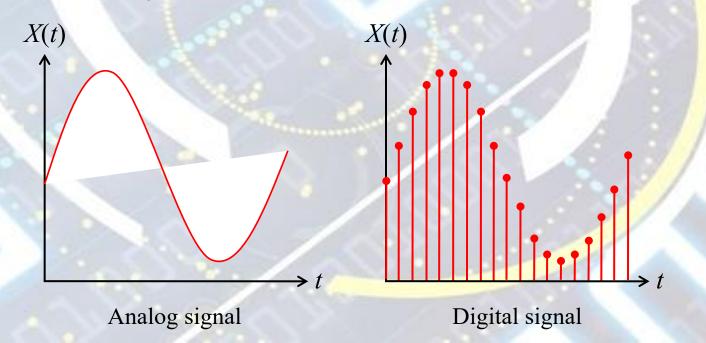

## Analog and Digital Signal

#### Analog system

The physical quantities or signals may vary continuously over a specified range.

#### Digital system

- The physical quantities or signals can assume only discrete values.

- Greater accuracy

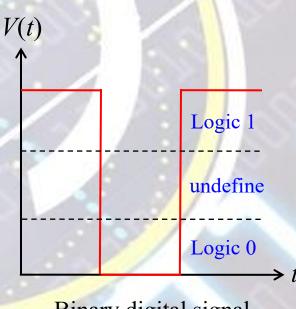

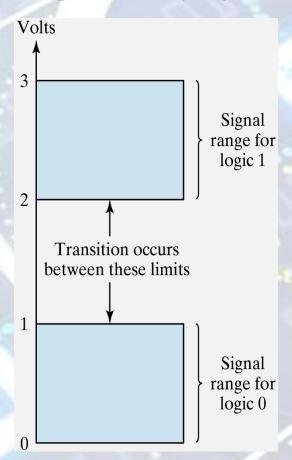

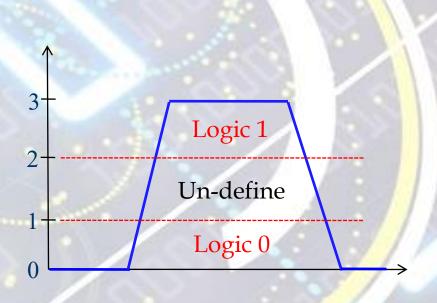

## Binary Digital Signal

- An information variable represented by physical quantity.

- For digital systems, the variable takes on discrete values.

- ♦ Two level, or binary values are the most prevalent values.

- Binary values are represented abstractly by:

- Digits 0 and 1

- Words (symbols) False (F) and True (T)

- Words (symbols) Low (L) and High (H)

- And words On and Off

- Binary values are represented by values or ranges of values of physical quantities.

- Why Digital

- Digital circuits are inexpensive

- Easy to reduce noise

- Great flexibility in the design.

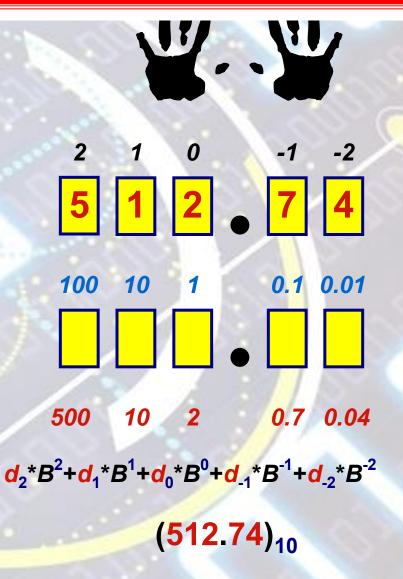

## Decimal Number System

- $\blacksquare$  Base (also called radix) = 10

- ◆ 10 digits { 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 }

- Digit Position

- Integer & fraction

- Digit Weight

- Weight =  $(Base)^{Position}$

- Magnitude

- Sum of "Digit x Weight"

- Formal Notation

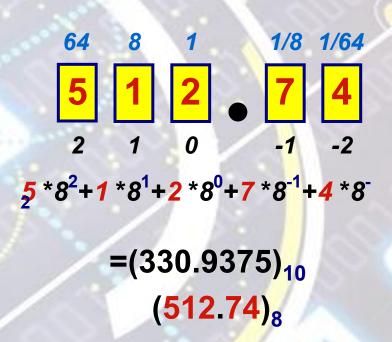

## Octal Number System

- **■** Base = 8

- ♦ 8 digits { 0, 1, 2, 3, 4, 5, 6, 7 }

- Weights

- Weight =  $(Base)^{Position}$

- Magnitude

- Sum of "Digit x Weight"

- Formal Notation

## Binary Number System

- **■** Base = 2

- $\bullet$  2 digits  $\{0, 1\}$ , called **b**inary dig**its** or "bits"

- Weights

- Weight =  $(Base)^{Position}$

- Magnitude

- Sum of "Bit x Weight"

- Formal Notation

- Groups of bits 4 bits = Nibble8 bits = Byte

1011

11000101

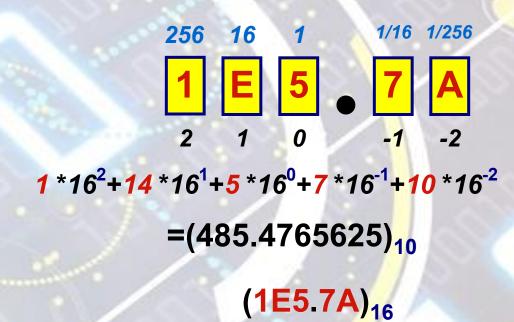

## Hexadecimal Number System

- **■** Base = 16

- ◆ 16 digits { 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F }

- Weights

- Weight =  $(Base)^{Position}$

- Magnitude

- Sum of "Digit x Weight"

- Formal Notation

## The Power of 2

| n | 2 <sup>n</sup> |

|---|----------------|

| 0 | $2^0=1$        |

| 1 | 21=2           |

| 2 | 22=4           |

| 3 | $2^3 = 8$      |

| 4 | 24=16          |

| 5 | 25=32          |

| 6 | 26=64          |

| 7 | 27=128         |

| n  | 2 <sup>n</sup>               |

|----|------------------------------|

| 8  | 28=256                       |

| 9  | 29=512                       |

| 10 | $2^{10} = \frac{1024}{1000}$ |

| 11 | 211=2048                     |

| 12 | 212=4096                     |

| 20 | $2^{20} = 1M$                |

| 30 | $2^{30} = 1G$                |

| 40 | 2 <sup>40</sup> =1T          |

Kilo

Mega

Giga

Tera

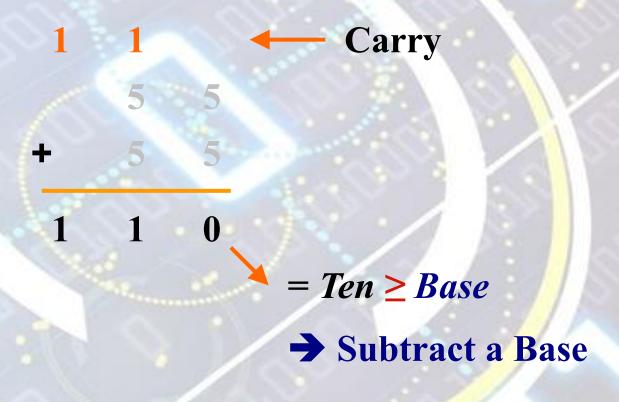

### Addition

Decimal Addition

## Binary Addition

■ Column Addition

$\geq (2)_{10}$

## Binary Subtraction

■ Borrow a "Base" when needed

## Binary Multiplication

■ Bit by bit

## Binary Division

■ Bit by bit

**Quotient value**

$$Q = 11$$

$$R = 11$$

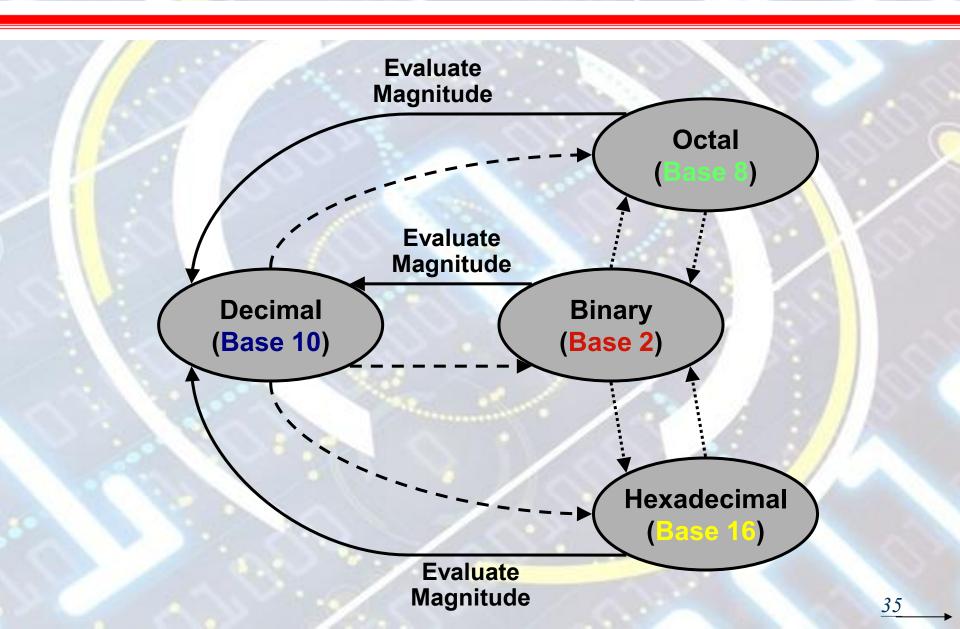

#### **Number Base Conversions**

## Week -2 Page(37-45)

## Decimal (Integer) to Binary Conversion

- Divide the number by the 'Base' (=2)

- Take the remainder (either 0 or 1) as a coefficient

- Take the quotient and repeat the division

#### **Example:** (13)<sub>10</sub>

|         |          |                 |                       | - 6 |

|---------|----------|-----------------|-----------------------|-----|

|         | Quotient | Remainder       | Coefficient           |     |

| 13/2=   | 6        | · 1 1           | $\mathbf{a_0} = 1$    |     |

| 6 / 2 = | 3        | 0               | $\mathbf{a_1} = 0$    |     |

| 3 / 2 = | 1        | 1               | $a_2 = 1$             |     |

| 1 / 2 = | 0        | 1               | $a_3 = 1$             |     |

| Answ    | er: (1:  | $(a_3 a_2 a_3)$ | $a_1 a_0)_2 = (1101)$ | 2   |

|         |          | 7               | 100                   |     |

|         |          | MSB             | LSB                   |     |

## Decimal (Fraction) to Binary Conversion

- Multiply the number by the 'Base' (=2)

- Take the integer (either 0 or 1) as a coefficient

- Take the resultant fraction and repeat the division

#### Example: (0.625)<sub>10</sub>

Integer Fraction Coefficient

$$0.625 * 2 = 1 . 25 a_{-1} = 1$$

$0.25 * 2 = 0 . 5 a_{-2} = 0$   $0.5 * 2 = 1 . 0 a_{-3} = 1$

Answer:

$$(0.625)_{10} = (0.a_{-1} a_{-2} a_{-3})_2 = (0.101)_2$$

MSB LSB

## Decimal to Octal Conversion

#### **Example:** (175)<sub>10</sub>

```

Quotient Remainder Coefficient 175/8 = 21 7 a_0 = 7 21/8 = 2 5 a_1 = 5 2/8 = 0 2 a_2 = 2

```

Answer:  $(175)_{10} = (a_2 a_1 a_0)_8 = (257)_8$

#### Example: $(0.3125)_{10}$

Integer Fraction Coefficient

$$0.3125 * 8 = 2 . 5 a_{-1} = 2 \ 0.5 * 8 = 4 . 0 a_{-2} = 4$$

Answer:  $(0.3125)_{10} = (0.a_{-1} a_{-2} a_{-3})_{8} = (0.24)_{8}$

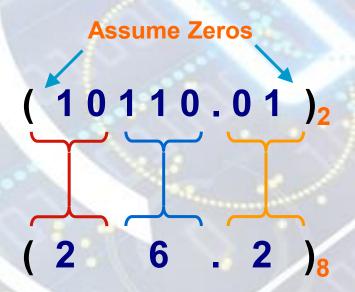

## Binary - Octal Conversion

- Each group of 3 bits represents an octal digit

Example:

| Octal | Binary |

|-------|--------|

| 0     | 0 0 0  |

| 1     | 0 0 1  |

| 2     | 010    |

| 3     | 011    |

| 4     | 100    |

| 5     | 1 0 1  |

| 6     | 110    |

| 7     | 111    |

Works both ways (Binary to Octal & Octal to Binary)

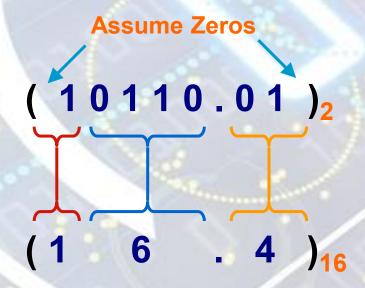

#### Binary - Hexadecimal Conversion

- $\blacksquare 16 = 2^4$

- Each group of 4 bits represents a hexadecimal digit

Example:

| Hex | Binary  |

|-----|---------|

| 0   | 0000    |

| 1   | 0 0 0 1 |

| 2   | 0010    |

| 3   | 0 0 1 1 |

| 4   | 0100    |

| 5   | 0101    |

| 6   | 0110    |

| 7   | 0 1 1 1 |

| 8   | 1000    |

| 9   | 1001    |

| A   | 1010    |

| В   | 1011    |

| C   | 1100    |

| D   | 1101    |

| Е   | 1110    |

| F   | 1111    |

Works both ways (Binary to Hex & Hex to Binary)

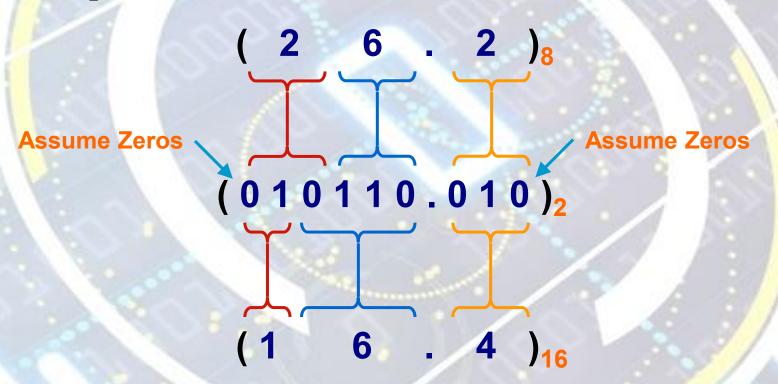

## Octal - Hexadecimal Conversion

Convert to Binary as an intermediate step

Example:

Works both ways (Octal to Hex & Hex to Octal)

# Decimal, Binary, Octal and Hexadecimal

| Decimal | Binary | Octal | Hex |

|---------|--------|-------|-----|

| 00      | 0000   | 00    | 0   |

| 01      | 0001   | 01    | 1   |

| 02      | 0010   | 02    | 2   |

| 03      | 0011   | 03    | 3   |

| 04      | 0100   | 04    | 4   |

| 05      | 0101   | 05    | 5   |

| 06      | 0110   | 06    | 6   |

| 07      | 0111   | 07    | 7   |

| 08      | 1000   | 10    | 8   |

| 09      | 1001   | 11    | 9   |

| 10      | 1010   | 12    | A   |

| 11      | 1011   | 13    | В   |

| 12      | 1100   | 14    | C   |

| 13      | 1101   | 15    | D   |

| 14      | 1110   | 16    | E   |

| 15      | 1111   | 17    | F   |

## 1.5 Complements

- There are two types of complements for each base-*r* system: the radix complement and diminished radix complement.

- **Diminished Radix Complement (r-1)'s Complement**

- Given a number N in base r having n digits, the (r-1)'s complement of N is defined as:

$$(r^n-1)-N$$

- **Example for 6-digit <u>decimal</u> numbers**:

- 9's complement is  $(r^n 1) N = (10^6 1) N = 999999 N$

- 9's complement of 546700 is 999999–546700 = 453299

- **Example for 7-digit binary numbers:**

- 1's complement is  $(r^n 1) N = (2^7 1) N = 11111111 N$

- → 1's complement of 1011000 is 1111111-1011000 = 0100111

- Observation:

- Subtraction from  $(r^n 1)$  will never require a borrow

- Diminished radix complement can be computed digit-by-digit

- For binary: 1 0 = 1 and 1 1 = 0

- 1's Complement (*Diminished Radix* Complement)

- ♦ All '0's become '1's

- ♦ All '1's become '0's

```

Example (10110000)_2

\Rightarrow (01001111)_2

```

If you add a number and its 1's complement ...

$\begin{array}{c} 1 \ 0 \ 1 \ 1 \ 0 \ 0 \ 0 \ 0 \\ + \ 0 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1 \ 1 \\ \hline 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \end{array}$

#### ■ Radix Complement

The r's complement of an n-digit number N in base r is defined as  $r^n - N$  for  $N \neq 0$  and as 0 for N = 0. Comparing with the (r - 1) 's complement, we note that the r's complement is obtained by adding 1 to the (r - 1) 's complement, since  $r^n - N = [(r^n - 1) - N] + 1$ .

**Example:** Base-10

The 10's complement of 012398 is 987602 The 10's complement of 246700 is 753300

**■** Example: Base-2

The 2's complement of 1101100 is 0010100 The 2's complement of 0110111 is 1001001

- 2's Complement (*Radix* Complement)

- → Take 1's complement then add 1

- Toggle all bits to the left of the first '1' from the right

#### Example:

Number:

1's Comp.:

|   | 10110000 | 10110000 |

|---|----------|----------|

|   | 01001111 |          |

| + | 1        |          |

|   | 01010000 | 01010000 |

#### Subtraction with Complements

- The subtraction of two n-digit unsigned numbers M-N in base r can be done as follows:

- 1. Add the minuend M to the r's complement of the subtrahend N. Mathematically,  $M + (r^n N) = M N + r^n$ .

- 2. If  $M \ge N$ , the sum will produce and end carry  $r^n$ , which can be discarded; what is left is the result M N.

- 3. If M < N, the sum does not produce an end carry and is equal to  $r^n (N M)$ , which is the r's complement of (N M). To obtain the answer in a familiar form, take the r's complement of the sum and place a negative sign in front.

#### ■ Example 1.5

♦ Using 10's complement, subtract 72532 – 3250.

$$M = 72532$$

10's complement of  $N = +96750$

Sum = 169282

Discard end carry  $10^5 = -100000$

Answer = 69282

#### ■ Example 1.6

♦ Using 10's complement, subtract 3250 – 72532.

$$M = 03250$$

10's complement of  $N = +27468$

Sum = 30718

There is no end carry.

#### **■** Example 1.7

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y; and (b) Y - X, by using 2's complement.

(a)

$$X = 1010100$$

$2$ 's complement of  $Y = +0111101$

$Sum = 10010001$

Discard end carry  $2^7 = -10000000$

Answer.  $X - Y = 0010001$

(b)

$$Y = 1000011$$

2's complement of  $X = +0101100$

Sum = 1101111

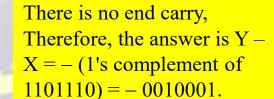

There is no end carry. Therefore, the answer is Y - X = -(2)'s complement of 11011111 = -0010001.

- Subtraction of unsigned numbers can also be done by means of the (r-1)'s complement. Remember that the (r-1) 's complement is one less then the r's complement.

- **Example** 1.8

- ♦ Repeat Example 1.7, but this time using 1's complement.

(a)

$$X-Y=1010100-1000011$$

$X=1010100$

1's complement of  $Y=\pm 0111100$

Sum = 10010000

End-around carry =  $\pm 1$

Answer.  $X-Y=0010001$

(b)

$$Y - X = 1000011 - 1010100$$

$Y = 1000011$

1's complement of  $X = \pm 0101011$

Sum = 1101110

# 1.6 Signed Binary Numbers

- To represent negative integers, we need a notation for negative values.

- It is customary to represent the sign with a bit placed in the leftmost position of the number since binary digits.

- The convention is to make the sign bit 0 for positive and 1 for negative.

- **■** Example:

| Signed-magnitude representation:      | 10001001 |

|---------------------------------------|----------|

| Signed-1's-complement representation: | 11110110 |

| Signed-2's-complement representation: | 11110111 |

■ Table 1.3 lists all possible four-bit signed binary numbers in the three representations.

# Signed Binary Numbers

**Table 1.3** *Signed Binary Numbers*

| Decimal   | Signed-2's<br>Complement | Signed-1's<br>Complement | Signed<br>Magnitude |

|-----------|--------------------------|--------------------------|---------------------|

| +7        | 0111                     | 0111                     | 0111                |

| +6        | 0110                     | 0110                     | 0110                |

| +5        | 0101                     | 0101                     | 0101                |

| +4        | 0100                     | 0100                     | 0100                |

| +3        | 0011                     | 0011                     | 0011                |

| +2        | 0010                     | 0010                     | 0010                |

| +1        | 0001                     | 0001                     | 0001                |

| +0        | 0000                     | 0000                     | 0000                |

| -0        | _                        | 1111                     | 1000                |

| -1        | 1111                     | 1110                     | 1001                |

| -2        | 1110                     | 1101                     | 1010                |

| -3        | 1101                     | 1100                     | 1011                |

| -4        | 1100                     | 1011                     | 1100                |

| -5        | 1011                     | 1010                     | 1101                |

| -6        | 1010                     | 1001                     | 1110                |

| <b>-7</b> | 1001                     | 1000                     | 1111                |

| -8        | 1000                     | _                        | _                   |

# Signed Binary Numbers

#### Arithmetic addition

- ◆ The addition of two numbers in the signed-magnitude system follows the rules of ordinary arithmetic. If the signs are the same, we add the two magnitudes and give the sum the common sign. If the signs are different, we subtract the smaller magnitude from the larger and give the difference the sign if the larger magnitude.

- ♦ The addition of two signed binary numbers with negative numbers represented in signed-2's-complement form is obtained from the addition of the two numbers, including their sign bits.

- A carry out of the sign-bit position is discarded.

#### Example:

| + 6        | 00000110        | - 6        | 11111010        |

|------------|-----------------|------------|-----------------|

| <u>+13</u> | 00001101        | <u>+13</u> | 00001101        |

| + 19       | 00010011        | + 7        | 00000111        |

| + 6        | 00000110        | -6         | 11111010        |

| <u>-13</u> | <u>11110011</u> | <u>-13</u> | <u>11110011</u> |

| <b>-</b> 7 | 11111001        | - 19       | 11101101        |

# Signed Binary Numbers

- Arithmetic Subtraction

- In 2's-complement form:

- 1. Take the 2's complement of the subtrahend (including the sign bit) and add it to the minuend (including sign bit).

- 2. A carry out of sign-bit position is discarded.

$$(\pm A) - (+B) = (\pm A) + (-B)$$

$$(\pm A) - (-B) = (\pm A) + (+B)$$

Example:

$$(-6)-(-13)$$

(11111010 - 11110011)

(11111010 + 00001101)

00000111 (+7)

# Week -4 Page(58-80) 57

## 1.7 Binary Codes

#### BCD Code

- A number with k decimal digits will require 4k bits in BCD.

- Decimal 396 is represented in BCD with 12bits as 0011 1001 0110, with each group of 4 bits representing one decimal digit.

- A decimal number in BCD is the same as its equivalent binary number only when the number is between 0 and 9.

- The binary combinations 1010

through 1111 are not used and have no meaning in BCD.

**Table 1.4** *Binary-Coded Decimal (BCD)*

| BCD<br>Digit |

|--------------|

| 0000         |

| 0001         |

| 0010         |

| 0011         |

| 0100         |

| 0101         |

| 0110         |

| 0111         |

| 1000         |

| 1001         |

|              |

- **Example:**

- Consider decimal 185 and its corresponding value in BCD and binary:

$$(185)_{10} = (0001\ 1000\ 0101)_{BCD} = (10111001)_2$$

BCD addition

#### Example:

$\bullet$  Consider the addition of 184 + 576 = 760 in BCD:

| BCD        | 1             | 1           |             |      |

|------------|---------------|-------------|-------------|------|

|            | 0001          | 1000        | 0100        | 184  |

|            | <u>+ 0101</u> | <u>0111</u> | <u>0110</u> | +576 |

| Binary sum | 0111          | 10000       | 1010        |      |

| Add 6      |               | <u>0110</u> | <u>0110</u> |      |

| BCD sum    | 0111          | 0110        | 0000        | 760  |

■ Decimal Arithmetic: (+375) + (-240) = +135

$$\begin{array}{rr}

0 & 375 \\

+9 & 760 \\

0 & 135

\end{array}$$

Hint 6: using 10's of BCD

#### Other Decimal Codes

**Table 1.5**Four Different Binary Codes for the Decimal Digits

| Decimal<br>Digit | BCD<br>8421 | 2421 | Excess-3 | 8, 4, -2, -1 |

|------------------|-------------|------|----------|--------------|

| 0                | 0000        | 0000 | 0011     | 0000         |

| 1                | 0001        | 0001 | 0100     | 0111         |

| 2                | 0010        | 0010 | 0101     | 0110         |

| 3                | 0011        | 0011 | 0110     | 0101         |

| 4                | 0100        | 0100 | 0111     | 0100         |

| 5                | 0101        | 1011 | 1000     | 1011         |

| 6                | 0110        | 1100 | 1001     | 1010         |

| 7                | 0111        | 1101 | 1010     | 1001         |

| 8                | 1000        | 1110 | 1011     | 1000         |

| 9                | 1001        | 1111 | 1100     | 1111         |

|                  | 1010        | 0101 | 0000     | 0001         |

| Unused           | 1011        | 0110 | 0001     | 0010         |

| bit              | 1100        | 0111 | 0010     | 0011         |

| combi-           | 1101        | 1000 | 1101     | 1100         |

| nations          | 1110        | 1001 | 1110     | 1101         |

|                  | 1111        | 1010 | 1111     | 1110         |

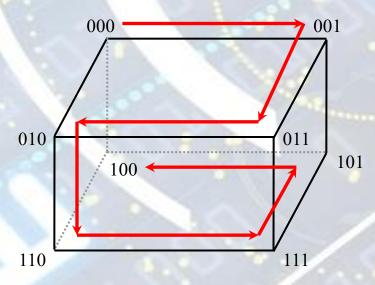

#### Gray Code

- ◆ The advantage is that only bit in the code group changes in going from one number to the next.

- » Error detection.

- » Representation of analog data.

- » Low power design.

1-1 and onto!!

**Table 1.6** *Gray Code*

| Gray<br>Code | Decimal<br>Equivalent |

|--------------|-----------------------|

| 0000         | 0                     |

| 0001         | 1                     |

| 0011         | 2                     |

| 0010         | 3                     |

| 0110         | 4                     |

| 0111         | 5                     |

| 0101         | 6                     |

| 0100         | 7                     |

| 1100         | 8                     |

| 1101         | 9                     |

| 1111         | 10                    |

| 1110         | 11                    |

| 1010         | 12                    |

| 1011         | 13                    |

| 1001         | 14                    |

| 1000         | 15                    |

American Standard Code for Information Interchange (ASCII) Character Code

**Table 1.7** *American Standard Code for Information Interchange (ASCII)*

|                | $b_7b_6b_5$ |     |     |     |     |          |     |     |

|----------------|-------------|-----|-----|-----|-----|----------|-----|-----|

| $b_4b_3b_2b_1$ | 000         | 001 | 010 | 011 | 100 | 101      | 110 | 111 |

| 0000           | NUL         | DLE | SP  | 0   | @   | P        | `   | p   |

| 0001           | SOH         | DC1 | !   | 1   | A   | Q        | a   | q   |

| 0010           | STX         | DC2 | "   | 2   | В   | R        | b   | r   |

| 0011           | ETX         | DC3 | #   | 3   | C   | S        | c   | S   |

| 0100           | EOT         | DC4 | \$  | 4   | D   | T        | d   | t   |

| 0101           | ENQ         | NAK | %   | 5   | E   | U        | e   | u   |

| 0110           | ACK         | SYN | &   | 6   | F   | V        | f   | V   |

| 0111           | BEL         | ETB | •   | 7   | G   | W        | g   | w   |

| 1000           | BS          | CAN | (   | 8   | Н   | X        | h   | X   |

| 1001           | HT          | EM  | )   | 9   | I   | Y        | i   | y   |

| 1010           | LF          | SUB | 344 | :   | J   | Z        | j   | z   |

| 1011           | VT          | ESC | +   | ;   | K   | [        | k   | {   |

| 1100           | FF          | FS  | ,   | <   | L   | \        | 1   | Ì   |

| 1101           | CR          | GS  | _   | =   | M   | ]        | m   | }   |

| 1110           | SO          | RS  |     | >   | N   | $\wedge$ | n   | ~   |

| 1111           | SI          | US  | /   | ?   | O   | _        | O   | DEL |

#### ■ ASCII Character Code

| Control characters |                     |     |                           |  |  |  |  |  |

|--------------------|---------------------|-----|---------------------------|--|--|--|--|--|

| NUL                | Null                | DLE | Data-link escape          |  |  |  |  |  |

| SOH                | Start of heading    | DC1 | Device control 1          |  |  |  |  |  |

| STX                | Start of text       | DC2 | Device control 2          |  |  |  |  |  |

| ETX                | End of text         | DC3 | Device control 3          |  |  |  |  |  |

| EOT                | End of transmission | DC4 | Device control 4          |  |  |  |  |  |

| ENQ                | Enquiry             | NAK | Negative acknowledge      |  |  |  |  |  |

| ACK                | Acknowledge         | SYN | Synchronous idle          |  |  |  |  |  |

| BEL                | Bell                | ETB | End-of-transmission block |  |  |  |  |  |

| BS                 | Backspace           | CAN | Cancel                    |  |  |  |  |  |

| HT                 | Horizontal tab      | EM  | End of medium             |  |  |  |  |  |

| LF                 | Line feed           | SUB | Substitute                |  |  |  |  |  |

| VT                 | Vertical tab        | ESC | Escape                    |  |  |  |  |  |

| FF                 | Form feed           | FS  | File separator            |  |  |  |  |  |

| CR                 | Carriage return     | GS  | Group separator           |  |  |  |  |  |

| SO                 | Shift out           | RS  | Record separator          |  |  |  |  |  |

| SI                 | Shift in            | US  | Unit separator            |  |  |  |  |  |

| SP                 | Space               | DEL | Delete                    |  |  |  |  |  |

#### **ASCII Character Codes**

- American Standard Code for Information Interchange (Refer to Table 1.7)

- A popular code used to represent information sent as character-based data.

- It uses 7-bits to represent:

- 94 Graphic printing characters.

- 34 Non-printing characters.

- Some non-printing characters are used for text format (e.g. BS = Backspace, CR = carriage return).

- Other non-printing characters are used for record marking and flow control (e.g. STX and ETX start and end text areas).

## **ASCII Properties**

- ASCII has some interesting properties:

- Digits 0 to 9 span Hexadecimal values 30<sub>16</sub> to 39<sub>16</sub>

- Upper case A-Z span 41<sub>16</sub> to 5A<sub>16</sub>

- Lower case a-z span 61<sub>16</sub> to 7A<sub>16</sub>

- » Lower to upper case translation (and vice versa) occurs by flipping bit 6.

#### ■ Error-Detecting Code

- To detect errors in data communication and processing, an <u>Eighth bit</u> is sometimes added to the ASCII character to indicate its parity.

- ◆ A parity bit is an extra bit included with a message to make the total number of 1's either even or odd.

#### **E**xample:

Consider the following two characters and their even and odd parity:

|                     | With even parity | With odd parity |

|---------------------|------------------|-----------------|

| ASCII $A = 1000001$ | 01000001         | 11000001        |

| ASCII $T = 1010100$ | 11010100         | 01010100        |

#### ■ Error-Detecting Code

- ◆ Redundancy (e.g. extra information), in the form of extra bits, can be incorporated into binary code words to detect and correct errors.

- A simple form of redundancy is parity, an extra bit appended onto the code word to make the number of 1's odd or even. Parity can detect all single-bit errors and some multiple-bit errors.

- ♦ A code word has even parity if the number of 1's in the code word is even.

- ♦ A code word has odd parity if the number of 1's in the code word is odd.

- Example:

Message A: 100010011 (even parity)

Message B: 100010010 (odd parity)

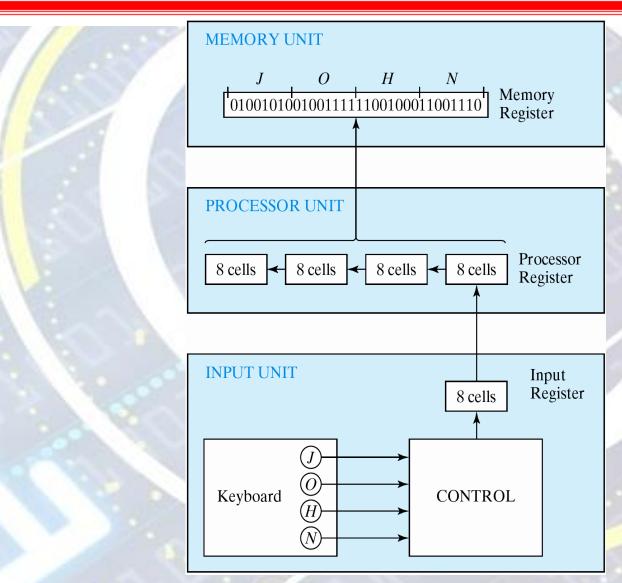

# 1.8 Binary Storage and Registers

#### Registers

- A binary cell is a device that possesses two stable states and is capable of storing one of the two states.

- ♦ A register is a group of binary cells. A register with *n* cells can store any discrete quantity of information that contains *n* bits.

n cells 2<sup>n</sup> possible states

#### A binary cell

- ♦ Two stable state

- Store one bit of information

- Examples: flip-flop circuits, ferrite cores, capacitor

#### A register

- A group of binary cells

- ♦ AX in x86 CPU

#### Register Transfer

- ♦ A transfer of the information stored in one register to another.

- One of the major operations in digital system.

- An example in next slides.

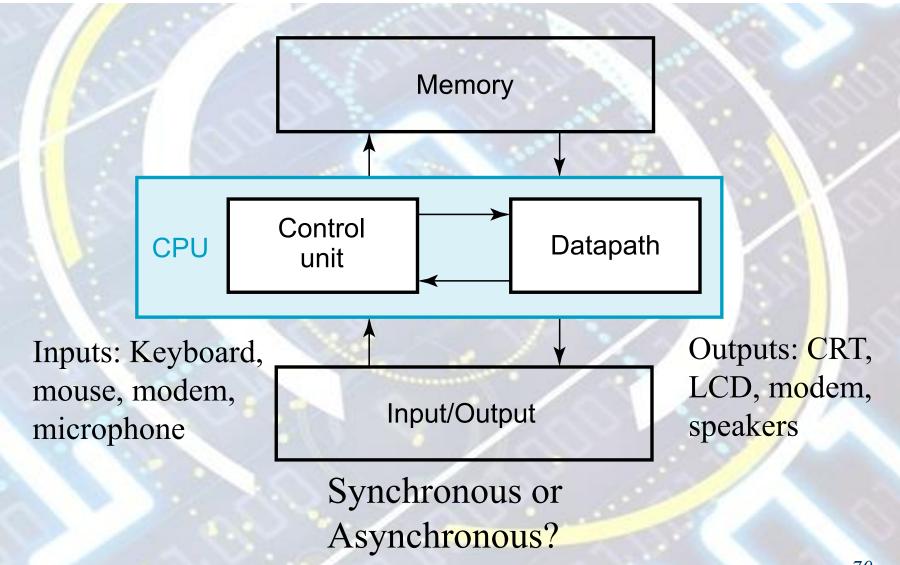

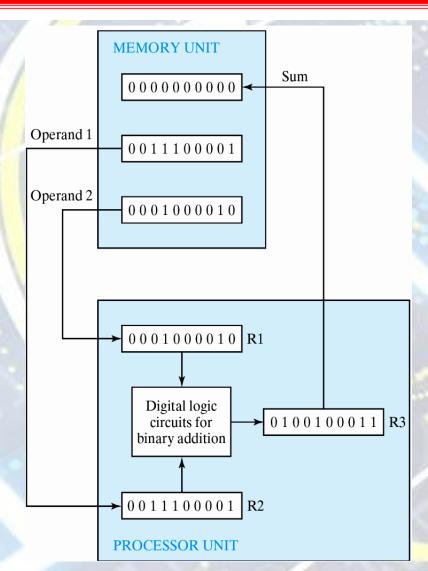

# A Digital Computer Example

## Transfer of information

Figure 1.1 Transfer of information among register

#### Transfer of information

- The other major component of a digital system

- Circuit elements to manipulate individual bits of information

- Load-store machine

```

LD R1;

LD R2;

ADD R2, R1;

SD R3;

```

Figure 1.2 Example of binary information processing

## 1.9 Binary Logic

#### Definition of Binary Logic

- Binary logic consists of binary variables and a set of logical operations.

- The variables are designated by letters of the alphabet, such as A, B, C, x, y, z, etc, with each variable having two and only two distinct possible values: 1 and 0,

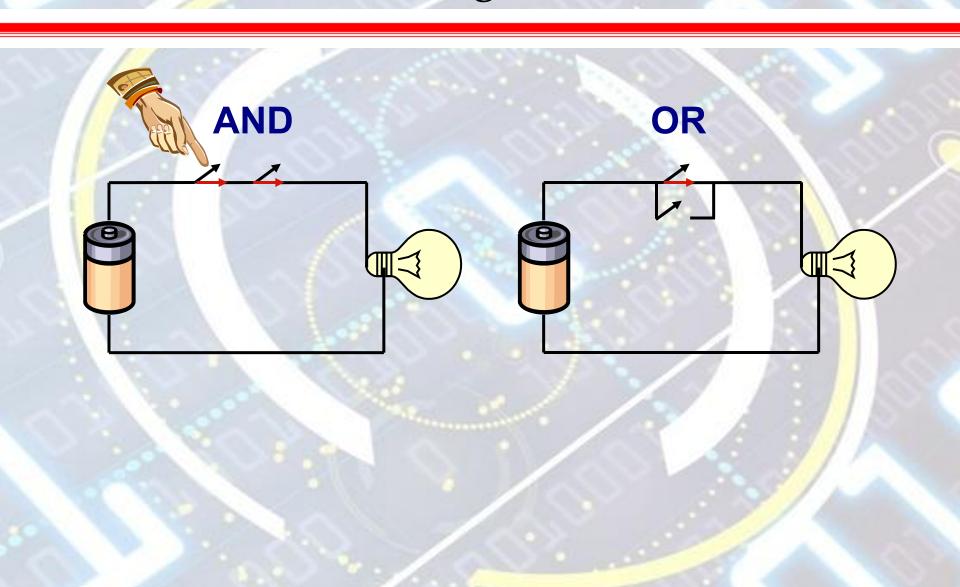

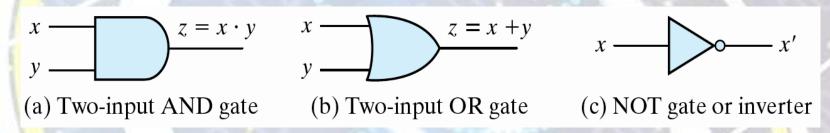

- ♦ Three basic logical operations: AND, OR, and NOT.

- 1. AND: This operation is represented by a dot or by the absence of an operator. For example,  $x \cdot y = z$  or xy = z is read "x AND y is equal to z," The logical operation AND is interpreted to mean that z = 1 if only x = 1 and y = 1; otherwise z = 0. (Remember that x, y, and z are binary variables and can be equal either to 1 or 0, and nothing else.)

- 2. OR: This operation is represented by a plus sign. For example, x + y = z is read "x OR y is equal to z," meaning that z = 1 if x = 1 or y = 1 or if both x = 1 and y = 1. If both x = 0 and y = 0, then z = 0.

- 3. NOT: This operation is represented by a prime (sometimes by an overbar). For example, x' = z (or  $\overline{x} = z$ ) is read "not x is equal to z," meaning that z is what z is not. In other words, if x = 1, then z = 0, but if x = 0, then z = 1, The NOT operation is also referred to as the complement operation, since it changes a 1 to 0 and a 0 to

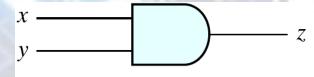

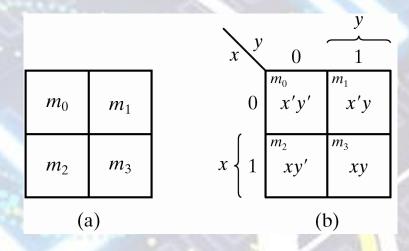

■ Truth Tables, Boolean Expressions, and Logic Gates

#### **AND**

| X | y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$z = x \bullet y = x y$$

$$x$$

$y$

$-z$

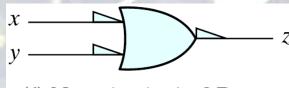

#### OR

| $\boldsymbol{x}$ | y | Z |

|------------------|---|---|

| 0                | 0 | 0 |

| 0                | 1 | 1 |

| 1                | 0 | 1 |

| 1                | 1 | 1 |

$$z = x + y$$

#### NOT

| X | Z |

|---|---|

| 0 | 1 |

| 1 | 0 |

$$z=\overline{x}=x'$$

$$x \longrightarrow z$$

■ Truth Tables, Boolean Expressions, and Logic Gates

#### **NAND**

| $\mathcal{X}$ | y | Z |

|---------------|---|---|

| 0             | 0 | 1 |

| 0             | 1 | 1 |

| 1             | 0 | 1 |

| 1             | 1 | 0 |

$$z=\overline{(x.y)}$$

### NOR

| X | y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

$$z = \overline{(x + y)}$$

■ Truth Tables, Boolean Expressions, and Logic Gates

#### **XOR**

| X | y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$z = \overline{x}.y + x.\overline{y}$$

#### **XNOR**

| X | y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$z = x. y + \overline{x. y}$$

# **Switching Circuits**

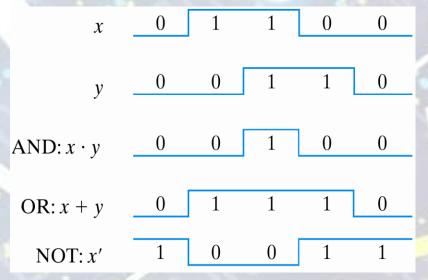

#### Logic gates

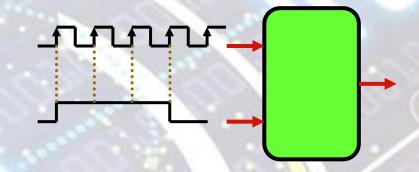

Example of binary signals

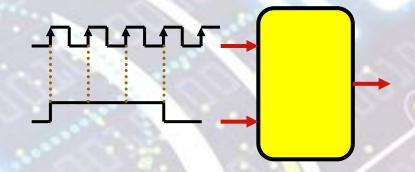

Figure 1.3 Example of binary signals

#### Logic gates

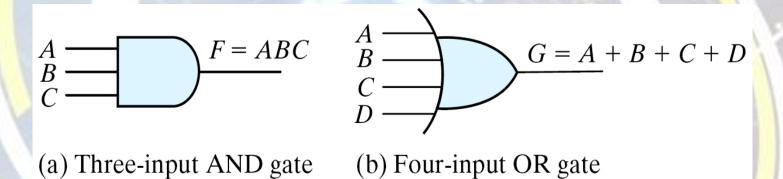

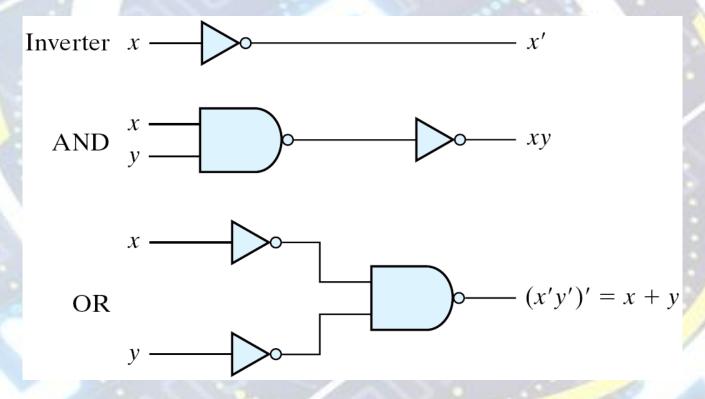

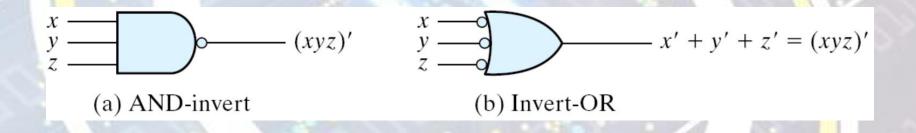

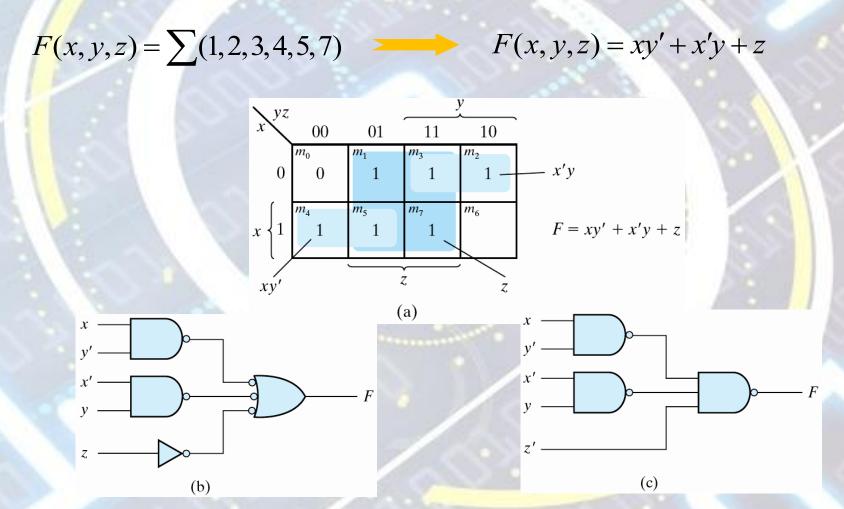

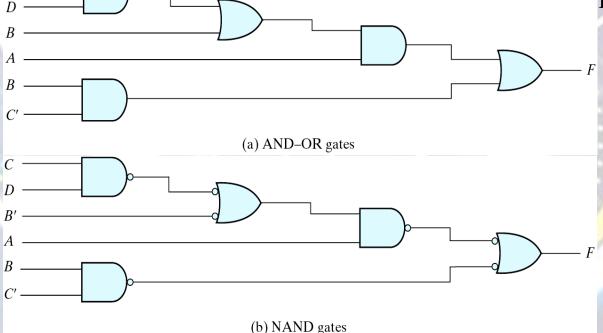

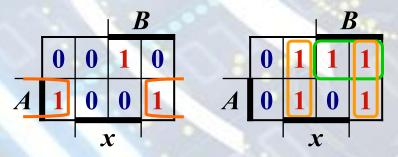

Graphic Symbols and Input-Output Signals for Logic gates:

Fig. 1.4 Symbols for digital logic circuits

Fig. 1.5 Input-Output signals for gates

#### Logic gates

Graphic Symbols and Input-Output Signals for Logic gates:

Fig. 1.6 Gates with multiple inputs

Week -6

Page(82-104)

# Algebras

- What is an algebra?

- Mathematical system consisting of

- » Set of elements

- » Set of operators

- » Axioms or postulates

- Why is it important?

- Defines rules of "calculations"

- Example: arithmetic on natural numbers

- Set of elements:  $N = \{1, 2, 3, 4, ...\}$

- ◆ Operator: +, -, \*

- Axioms: associativity, distributivity, closure, identity elements, etc.

- Note: operators with two inputs are called *binary*

- Does not mean they are restricted to binary numbers!

- Operator(s) with one input are called unary

## **BASIC DEFINITIONS**

- A set is collection of having the same property.

- $\diamond$  S: set, x and y: element or event

- For example:  $S = \{1, 2, 3, 4\}$

- » If x = 2, then  $x \in S$ .

- » If y = 5, then  $y \notin S$ .

- A *binary operator* defines on a set *S* of elements is a rule that assigns, to each pair of elements from *S*, a unique element from *S*.

- For example: given a set S, consider a\*b = c and \* is a binary operator.

- We say that, \* is a binary operator if it is specifies a rule for finding c from the pair (a, b) and also if  $a, b, c \in S$ .

- ♦ On the other hand, \* is not a binary operator if  $a, b \in S$ , while the rule finds  $c \notin S$ .

## **BASIC DEFINITIONS**

- The most common postulates used to formulate various algebraic structures are as follows:

- 1. Closure: a set S is closed with respect to a binary operator if, for every pair of elements of S, the binary operator specifies a rule for obtaining a unique element of S.

- ♦ For example, natural numbers  $N = \{1, 2, 3, ...\}$  is closed w.r.t. the binary operator + by the rule of arithmetic addition, since, for any  $a, b \in N$ , there is a unique  $c \in N$  such that

- a+b=c

- » But operator is not closed for N, because 2-3 = -1 and 2, 3  $\in N$ , but  $(-1)\notin N$ .

- 2. Associative law: a binary operator \* on a set S is said to be associative whenever

- (x \* y) \* z = x \* (y \* z) for all  $x, y, z \in S$ • (x+y)+z = x+(y+z)

- 3. Commutative law: a binary operator \* on a set S is said to be commutative whenever

## **BASIC DEFINITIONS**

- 4. Identity element: a set S is said to have an identity element with respect to a binary operation \* on S if there exists an element  $e \in S$  with the property that

- $\bullet$  e \* x = x \* e = x for every  $x \in S$

- »  $\theta + x = x + \theta = x$  for every  $x \in I$ .  $I = \{..., -3, -2, -1, 0, 1, 2, 3, ...\}$ .

- » I \* x = x \* I = x for every  $x \in I$ .  $I = \{..., -3, -2, -1, 0, 1, 2, 3, ...\}$ .

- 5. Inverse: a set having the identity element e with respect to the binary operator to have an inverse whenever, for every  $x \in S$ , there exists an element  $y \in S$  such that

- x \* y = e

- » The operator + over I, with e = 0, the inverse of an element a is (-a), since a + (-a) = 0.

- 6. Distributive law: if \* and · are two binary operators on a set S, \* is said to be distributive over . whenever

- $x * (y \cdot z) = (x * y) \cdot (x * z)$

# George Boole

#### ■ Father of Boolean algebra

- He came up with a type of linguistic algebra, the three most basic operations of which were (and still are) AND, OR and NOT. It was these three functions that formed the basis of his premise, and were the only operations necessary to perform comparisons or basic mathematical functions.

- Boole's system (detailed in his 'An Investigation of the Laws of Thought, on Which Are Founded the Mathematical Theories of Logic and Probabilities', 1854) was based on a binary approach, processing only two objects the yes-no, true-false, on-off, zero-one approach.

- Surprisingly, given his standing in the academic community, Boole's idea was either criticized or completely ignored by the majority of his peers.

- Eventually, one bright student, Claude Shannon (1916-2001), picked up the idea and ran with it

George Boole (1815 - 1864)

## Axiomatic Definition of Boolean Algebra

- We need to define algebra for binary values

- Developed by George Boole in 1854

- Huntington postulates for Boolean algebra (1904):

- $\blacksquare$   $B = \{0, 1\}$  and two binary operations, + and  $\cdot$

- Closure with respect to operator + and operator ·

- Identity element 0 for operator + and 1 for operator ·

- Commutativity with respect to + and ·

$$x+y=y+x$$

,  $x\cdot y=y\cdot x$

Distributivity of · over +, and + over ·

$$x \cdot (y+z) = (x \cdot y) + (x \cdot z)$$

and  $x + (y \cdot z) = (x+y) \cdot (x+z)$

- Complement for every element x is x' with x+x'=1,  $x\cdot x'=0$

- ♦ There are at least two elements  $x, y \in B$  such that  $x \neq y$

# Boolean Algebra

#### ■ Terminology:

- ♦ *Literal*: A variable or its complement

- ♦ Product term: literals connected by •

- → Sum term: literals connected by +

# Postulates of Two-Valued Boolean Algebra

- $\blacksquare$   $B = \{0, 1\}$  and two binary operations, + and  $\cdot$

- The rules of operations: AND · OR and NOT.

|   | AND |       |

|---|-----|-------|

| X | У   | x · y |

| 0 | 0   | 0     |

| 0 | 1   | 0     |

| 1 | 0   | 0     |

| 1 | 1   | 1     |

|   | <u>UK</u> |     |

|---|-----------|-----|

| Χ | У         | x+y |

| 0 | 0         | 0   |

| 0 | 1         | 1   |

| 1 | 0         | 1   |

| 1 | 1         | 1   |

| NOT |   |        |  |

|-----|---|--------|--|

| 3   | X | X'     |  |

|     | 0 | 1      |  |

|     | 1 | 0      |  |

|     |   | 100000 |  |

- 1. Closure (+ and·)

- 2. The identity elements

- (1) +: 0

- $(2) \cdot : 1$

# Postulates of Two-Valued Boolean Algebra

- 3. The commutative laws

- 4. The distributive laws

| x | y | z | y+z | $x \cdot (y+z)$ | $x \cdot y$ | $x \cdot z$ | $(x \cdot y) + (x \cdot z)$ |

|---|---|---|-----|-----------------|-------------|-------------|-----------------------------|

| 0 | 0 | 0 | 0   | 0               | 0           | 0           | 0                           |

| 0 | 0 | 1 | 1   | 0               | 0           | 0           | 0                           |

| 0 | 1 | 0 | 1   | 0               | 0           | 0           | 0                           |

| 0 | 1 | 1 | 1   | 0               | 0           | 0           | 0                           |

| 1 | 0 | 0 | 0   | 0               | 0           | 0           | 0                           |

| 1 | 0 | 1 | 1   | 1               | 0           | 1           | 1                           |

| 1 | 1 | 0 | 1   | 1               | 1           | 0           | 1                           |

| 1 | 1 | 1 | 1   | 1               | 1           | 1           | 1                           |

# Postulates of Two-Valued Boolean Algebra

- 5. Complement

- $x+x'=1 \rightarrow 0+0'=0+1=1; 1+1'=1+0=1$

- $\bullet$   $x \cdot x' = 0 \rightarrow 0 \cdot 0' = 0 \cdot 1 = 0; 1 \cdot 1' = 1 \cdot 0 = 0$

- 6. Has two distinct elements 1 and 0, with  $0 \neq 1$

- Note

- A set of two elements

- → +: OR operation; ·: AND operation

- A complement operator: NOT operation

- Binary logic is a two-valued Boolean algebra

## Duality

- The principle of *duality* is an important concept. This says that if an expression is valid in Boolean algebra, the dual of that expression is also valid.

- To form the dual of an expression, replace all + operators with . operators, all . operators with + operators, all ones with zeros, and all zeros with ones.

- Form the dual of the expression a + (b.c) = (a + b).(a + c)

- Following the replacement rules... a.(b+c) = a.b + a.c

- Take care not to alter the location of the parentheses if they are present.

#### **Basic Theorems**

**Table 2.1**Postulates and Theorems of Boolean Algebra

| Postulate 2               | (a) 	 x + 0 = x                 | (b) $x \cdot 1 = x$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Postulate 5               | (a) $x + x' = 1$                | (b) $x \cdot x' = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Theorem 1                 | (a) $x + x = x$                 | (b) $x \cdot x = x$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Theorem 2                 | (a) $x + 1 = 1$                 | (b) $x \cdot 0 = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Theorem 3, involution     | (x')' = x                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Postulate 3, commutative  | (a) 	 x + y = y + x             | (b) $xy = yx$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Theorem 4, associative    | (a) $x + (y + z) = (x + y) + z$ | (b) $x(yz) = (xy)z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Postulate 4, distributive | (a) 	 x(y+z) = xy + xz          | (b) $x + yz = (x + y)(x + z)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Theorem 5, DeMorgan       | (a) $(x + y)' = x'y'$           | (b) $(xy)' = x' + y'$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |